# MC68 = Z328 DragonBall-EZ™

Integrated Processor User's Manual

Order this document by MC68EZ328UM/D (Motorola Order Number) Rev. 1, 11/98

# MC68EZ328 Integrated Processor User's Manual

©MOTOROLA INC., 1998. All rights reserved. This document contains information on a new product. Specifications and information herein are subject to change without notice. Motorola reserves the right to make changes without further notice to any products herein to improve

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and A are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer

OnCE and Mfax are trademarks of Motorola, Inc.

## **TABLE OF CONTENTS**

| Paragrap<br>Number                                                                                                    | h<br>Title                                                                                                                                                                                                                                                                                                                                                                                                                       | Page<br>Number                                              |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|                                                                                                                       | PREFACE                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                             |

|                                                                                                                       | d Documentationization of This Manual                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |

|                                                                                                                       | SECTION 1 BASIC ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |

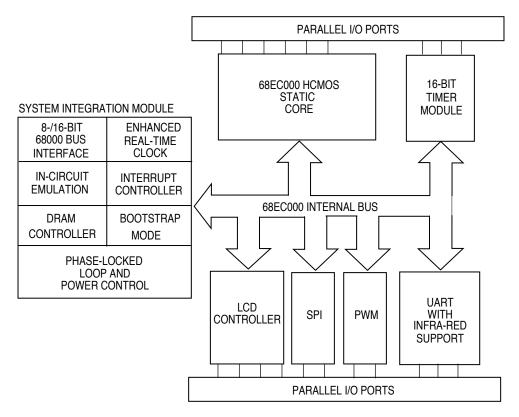

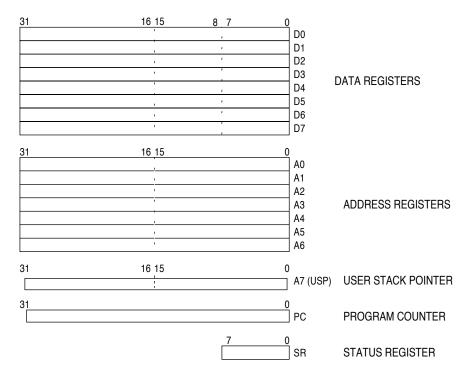

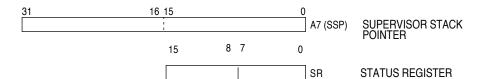

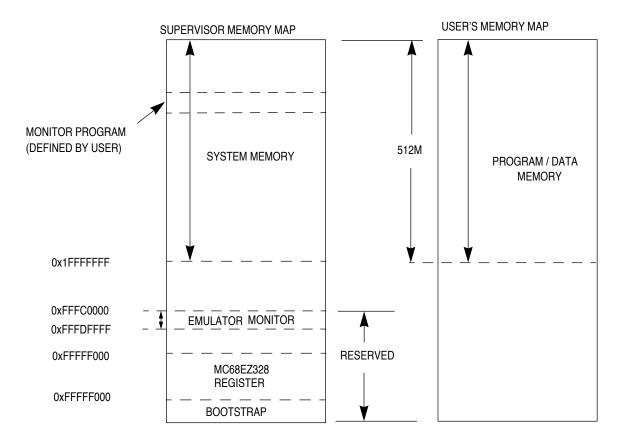

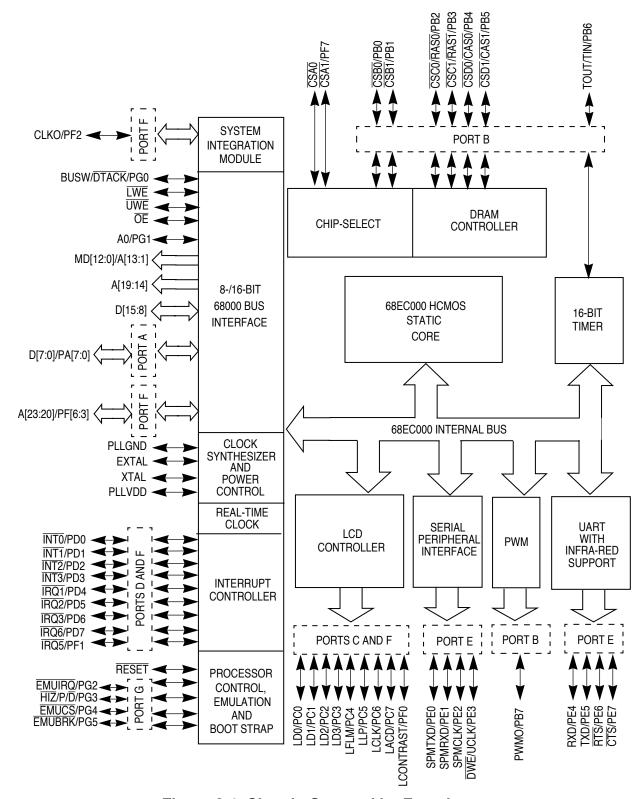

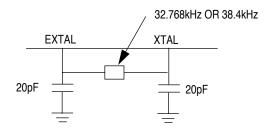

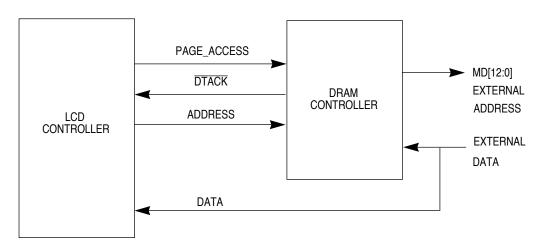

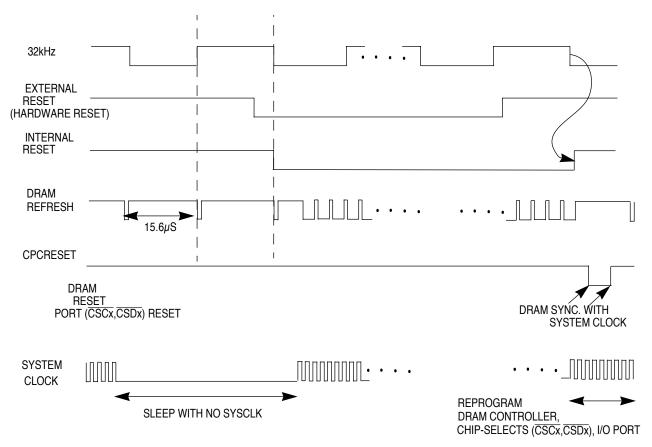

| 1.1<br>1.1.2<br>1.1.3<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8<br>1.9<br>1.10<br>1.11<br>1.12<br>1.13<br>1.14 | Core Programming Model Data and Address Mode Types. EC000 Instruction Set Chip-Select Logic and Bus Interface Phase-Locked Loop and Power Control Interrupt Controller Parallel General-Purpose I/O Ports Pulse-Width Modulator General-Purpose Timer Serial Peripheral Interface UART and Infra-Red Communication Support LCD Controller Real-Time Clock DRAM Controller In-Circuit Emulation Module Bootstrap Mode Memory Map. | 1-2 1-4 1-5 1-6 1-6 1-7 1-7 1-7 1-7 1-7 1-8 1-8 1-8 1-8 1-8 |

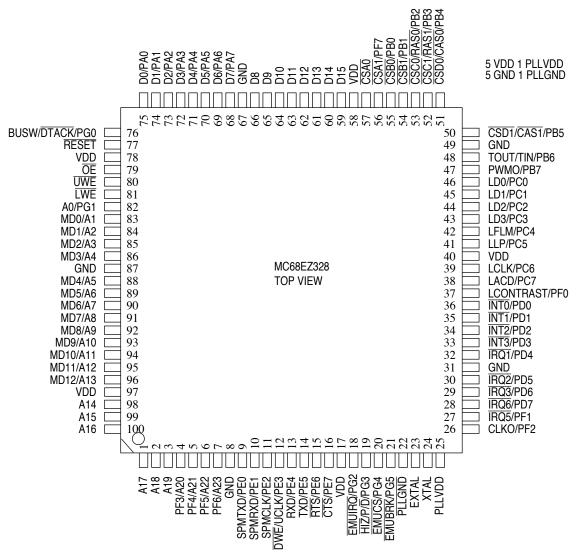

|                                                                                                                       | SECTION 2 SIGNAL DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                    |                                                             |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8                                                                  | Signals GROUped by Function POWER and Ground Signals CLOCK and System Control Signals ADDRESS BUS Signals DATA BUS Signals BUS CONTROL Signals INTERRUPT CONTROLIER Signals LCD CONTROLLER Signals                                                                                                                                                                                                                               | 2-4<br>2-4<br>2-5<br>2-5<br>2-6<br>2-6                      |

| 2.9<br>2.10<br>2.11<br>2.12<br>2.13<br>2.14 | UART Controller Signals2TIMER Signal2Pulse-Width Modulator Signal2Serial Peripheral Interface Signals2CHIP-SELECT Signals2In-Circuit EMULATion Signals2 | 2-8<br>2-8<br>2-8<br>2-9 |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|                                             | SECTION 3 SYSTEM CONTROL                                                                                                                                |                          |

| 3.1                                         | Operation                                                                                                                                               |                          |

| 3.2<br>3.2.1                                | Programming Model                                                                                                                                       |                          |

|                                             | SECTION 4                                                                                                                                               |                          |

|                                             | CHIP-SELECT LOGIC                                                                                                                                       |                          |

| 4.1                                         | Chip-Select Operation                                                                                                                                   |                          |

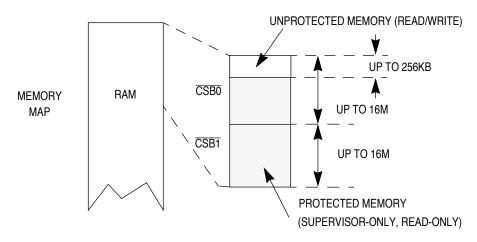

| 4.1.1<br>4.1.2                              | Memory Protection                                                                                                                                       |                          |

| 4.1.2                                       | Programmable Data Bus Size                                                                                                                              |                          |

| 4.2                                         | PROGRAMMING MODEL                                                                                                                                       |                          |

| 4.2.1                                       | Chip-Select Group Base Address Registers                                                                                                                |                          |

| 4.2.2                                       | Chip-Select Registers                                                                                                                                   |                          |

| 4.2.3                                       | Emulation Chip-Select Register                                                                                                                          |                          |

| 4.3                                         | Programming Example                                                                                                                                     | <b>I-9</b>               |

|                                             | SECTION 5                                                                                                                                               |                          |

|                                             | PHASE-LOCKED LOOP AND POWER CONTROL                                                                                                                     |                          |

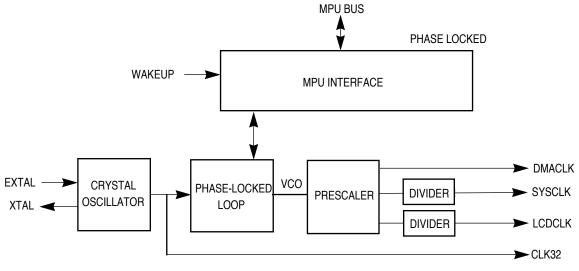

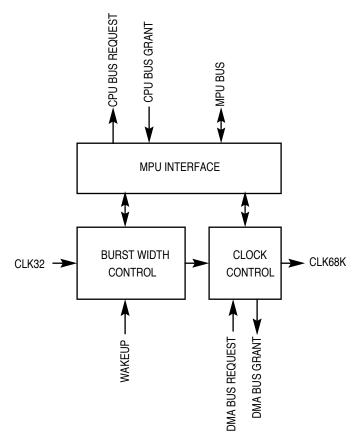

|                                             | Operation                                                                                                                                               |                          |

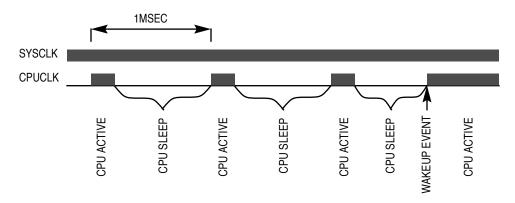

|                                             | Using the PLL To Reduce Power Consumption                                                                                                               |                          |

| 5.1.2                                       | PLL Operation at Power-Up                                                                                                                               |                          |

| 5.1.3                                       | PLL Operation at Wake-Up                                                                                                                                |                          |

| 5.1.4<br>5.1.5                              | Changing the VCO Frequency                                                                                                                              |                          |

| 5.2                                         | Programming Model                                                                                                                                       |                          |

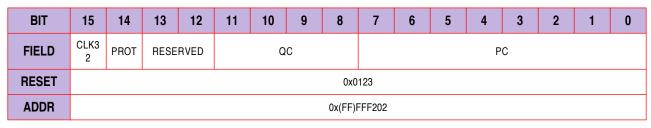

| 5.2.1                                       | PLL Control Register                                                                                                                                    |                          |

| 5.2.2                                       | PLL Frequency Select Register                                                                                                                           |                          |

| 5.3                                         | POWER CONTROL                                                                                                                                           |                          |

| 5.3.1                                       | Operating the Power Control Module                                                                                                                      |                          |

| 5.3.2                                       | Power Control Register5                                                                                                                                 | 5-9                      |

|                                             | OFOTION C                                                                                                                                               |                          |

## SECTION 6 INTERRUPT CONTROLLER

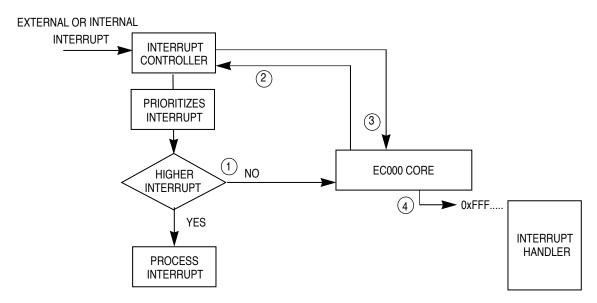

| 6.1          | Interrupt Processing                     |      |

|--------------|------------------------------------------|------|

| 6.2          | Exception Vectors                        |      |

| 6.3          | DATA BUS WIDTH FOR BOOT DEVICE OPERATION | 6-4  |

| 6.4          | INTERRUPT CONTROLLER operation           |      |

| 6.5          | Vector Generator                         |      |

| 6.6          | Programming Model                        |      |

| 6.6.1        | Interrupt Vector Register                |      |

| 6.6.2        | Interrupt Control Register               |      |

| 6.6.3        | Interrupt Mask Register                  |      |

| 6.6.4        | Interrupt Status Register                | 6-11 |

| 6.6.5        | Interrupt Pending Register               |      |

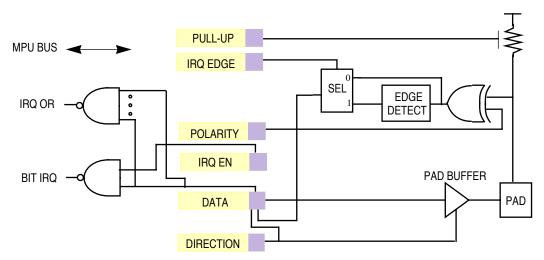

| 6.7          | KEYBOARD INTERRUPTs                      |      |

| 6.8          | PEN Interrupts                           | 6-20 |

|              | OFOTION 7                                |      |

|              | SECTION 7                                |      |

|              | PARALLEL PORTS                           |      |

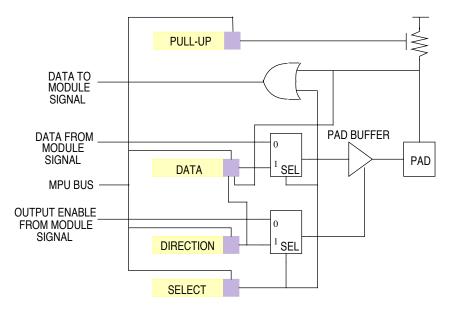

| 7.1          | Operation                                | 7-1  |

| 7.2          | Programming Model                        | 7-2  |

| 7.2.1        | Port A Registers                         |      |

| 7.2.2        | Port B Registers                         | 7-3  |

| 7.2.3        | Port C Registers                         |      |

| 7.2.4        | Port D Registers                         |      |

| 7.2.5        | Port E Registers                         |      |

| 7.2.6        | Port F Registers                         |      |

| 7.2.7        | Port G Registers                         | /-14 |

|              | SECTION 8                                |      |

|              | PULSE-WIDTH MODULATOR                    |      |

| 0.4          | Onevation                                | 0.4  |

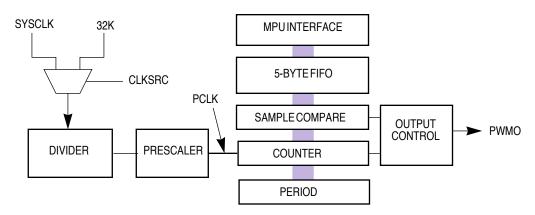

| 8.1<br>8.1.1 | Operation                                | 8-1  |

| 8.1.2        | Tone Mode                                |      |

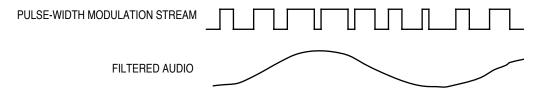

| 8.1.3        | D/A Mode                                 |      |

| 8.2          | Programming Model                        |      |

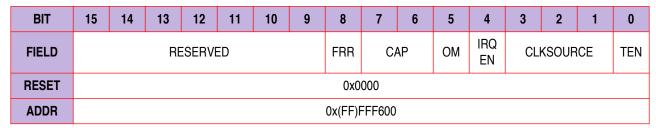

| 8.2.1        | PWM Control Register                     |      |

| 8.2.2        | PWM Sample Register                      |      |

| 8.2.3        | PWM Period Register                      | 8-5  |

| 8.2.4        | PWM Counter Register                     |      |

| 8.3          | Programming Example                      | 8-6  |

|              | SECTION 9                                |      |

|              | GENERAL-PURPOSE TIMER                    |      |

|              |                                          |      |

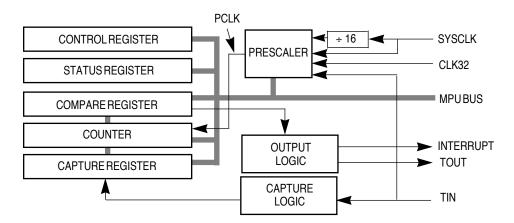

| 9.1          | OPERATION                                | 9-1  |

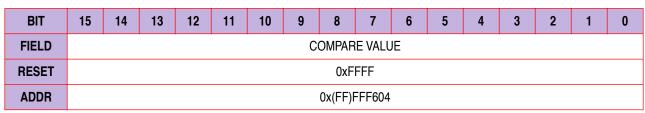

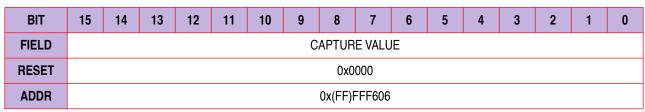

| 9.2<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.2.5<br>9.2.6                                                        | Programming Model 9-2 Timer Control Register 9-2 Timer Prescaler Register 9-2 Timer Compare Register 9-2 Timer Capture Register 9-2 Timer Counter Register 9-2 Timer Status Register 9-2                                                                                                      | 2<br>4<br>4<br>5 |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|                                                                                                                  | SECTION 10<br>SERIAL PERIPHERAL INTERFACE MASTER                                                                                                                                                                                                                                              |                  |

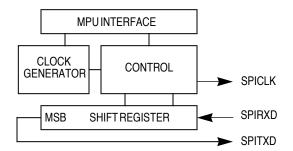

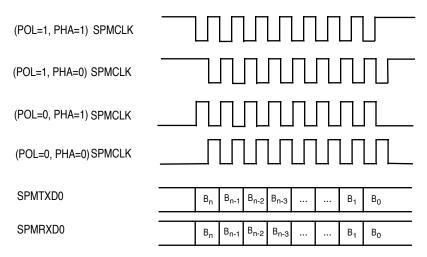

| 10.1<br>10.1.1<br>10.1.2<br>10.2<br>10.2.1<br>10.2.2                                                             | Signals                                                                                                                                                                                                                                                                                       | 2<br>3<br>3<br>4 |

| 1                                                                                                                | SECTION 11<br>UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER                                                                                                                                                                                                                                     |                  |

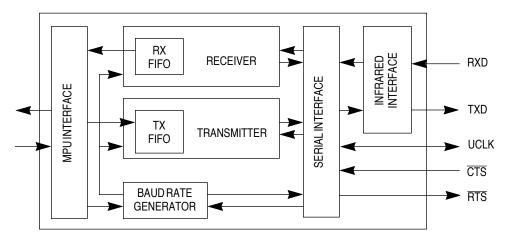

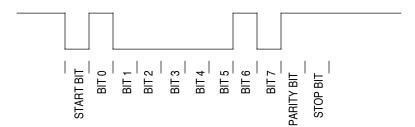

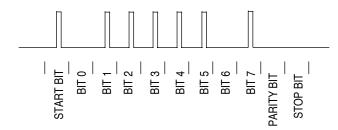

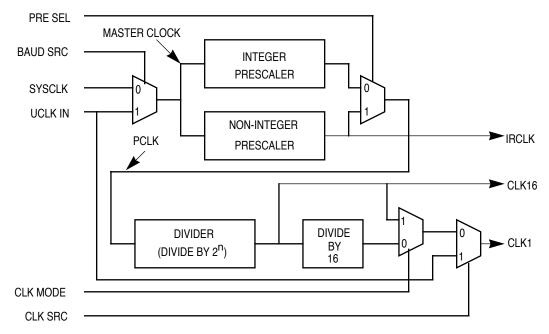

| 11.1<br>11.1.1<br>11.1.3<br>11.2<br>11.2.3<br>11.2.3<br>11.3.1<br>11.3.3<br>11.3.4<br>11.3.5<br>11.3.6<br>11.3.6 | IrDA Mode11-2SERIAL INTERFACE SIGNALS11-3SUB-BLOCK Operation11-4Transmitter11-4Receiver11-5Baud Rate Generator11-6Programming Model11-6UART Status/Control Register11-1UART Baud Control Register11-1UART Receiver Register11-1UART Transmitter Register11-14UART Miscellaneous Register11-14 | 22344568812468   |

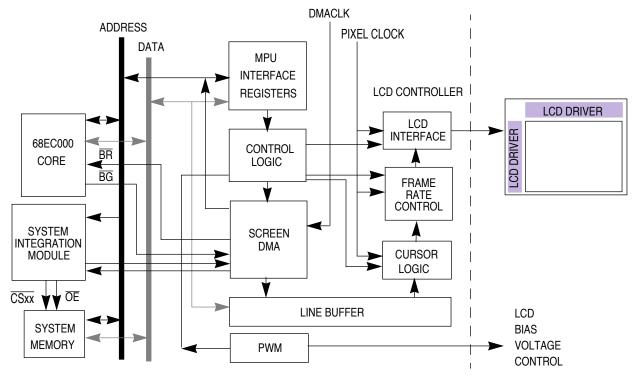

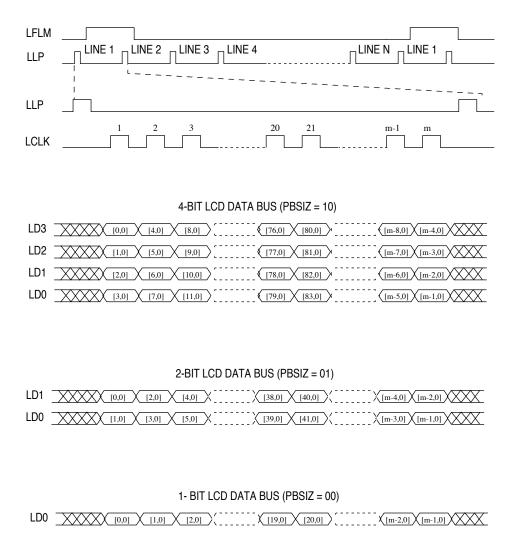

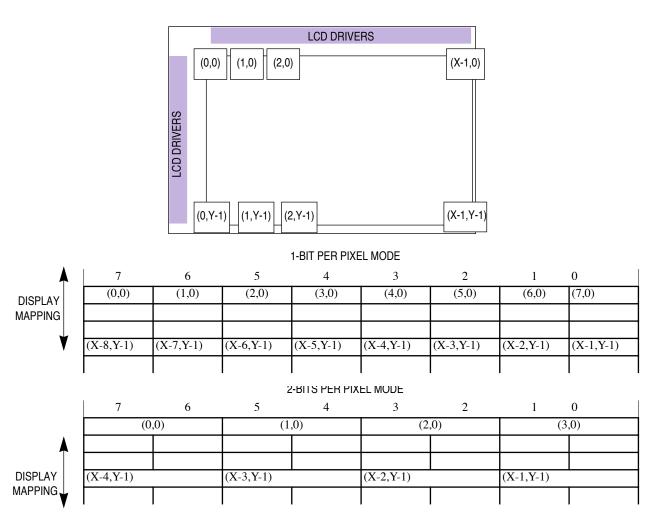

| 12.1<br>12.1.1<br>12.1.2<br>12.1.3                                                                               | Controlling the Display                                                                                                                                                                                                                                                                       | 3<br>4           |

| 12.1.4  | Using the DMA Controller                   | 12-8  |

|---------|--------------------------------------------|-------|

|         | Programming Model                          |       |

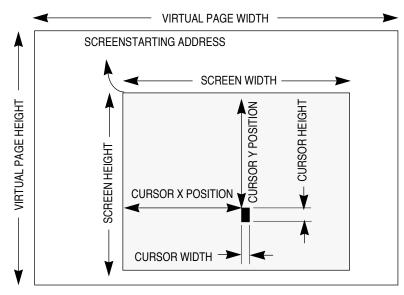

| 12.2.1  | LCD Screen Starting Address Register       |       |

| 12.2.2  | LCD Virtual Page Width Register            |       |

| 12.2.3  | LCD Screen Width Register                  |       |

| 12.2.4  | LCD Screen Height Register                 |       |

| 12.2.5  | LCD Cursor X Position Register             | 12-11 |

| 12.2.6  | LCD Cursor Y Position Register             |       |

| 12.2.7  | LCD Cursor Width and Height Register       | 12-12 |

| 12.2.8  | LCD Blink Control Register                 | 12-13 |

| 12.2.9  | LCD Panel Interface Configuration Register | 12-13 |

| 12.2.10 | LCD Polarity Configuration Register        | 12-14 |

| 12.2.11 |                                            |       |

| 12.2.12 | 2 LCD Pixel Clock Divider Register         | 12-15 |

| 12.2.13 | 3                                          |       |

| 12.2.14 |                                            |       |

| 12.2.15 |                                            |       |

| 12.2.16 |                                            |       |

| 12.2.17 | , , , , , , , , , , , , , , , , , , , ,    |       |

| 12.2.18 |                                            |       |

| 12.3 F  | Programming EXAMPLE                        | 12-19 |

|         | CECTION 40                                 |       |

|         | SECTION 13                                 |       |

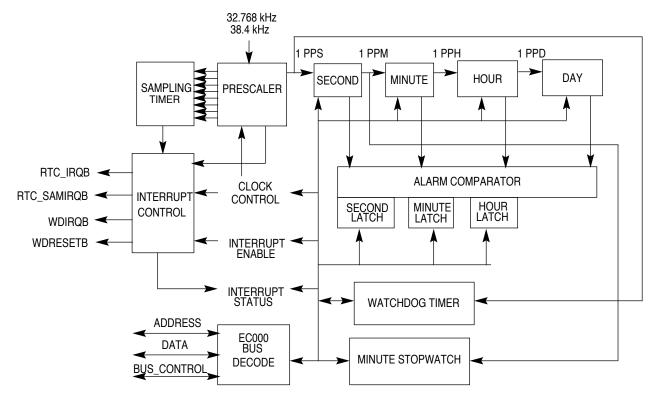

|         | REAL-TIME CLOCK                            |       |

| 13.1 (  | Operation                                  | 13-2  |

| 13.1.1  | Prescaler and Counter                      |       |

| 13.1.2  | Alarm                                      |       |

| 13.1.3  | Watchdog Timer                             |       |

| 13.1.4  | Sampling Timer                             |       |

| 13.1.5  | Minute Stopwatch                           |       |

|         | Programming Model                          |       |

| 13.2.1  | RTC Hours, Minutes, and Seconds Register   |       |

| 13.2.2  | RTC Alarm Register                         |       |

| 13.2.3  | Watchdog Timer Register                    |       |

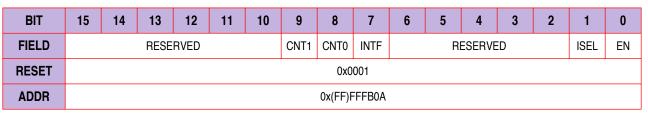

| 13.2.4  | RTC Control Register                       |       |

| 13.2.5  | RTC Interrupt Status Register              |       |

| 13.2.6  | RTC Interrupt Enable Register              |       |

| 13.2.7  | Stopwatch Minutes Register                 |       |

| 13.2.8  | RTC Day Count Register                     |       |

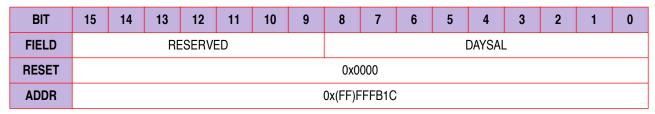

| 13.2.9  | RTC Day Alarm Register                     |       |

|         | ,                                          |       |

|         | SECTION 14                                 |       |

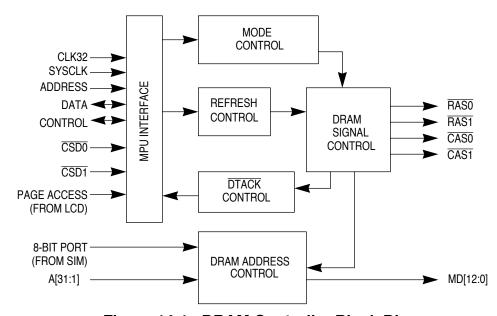

|         | DRAM CONTROLLER                            |       |

|         |                                            |       |

| 14.1 (  | OPERATION                                  | 14-2  |

| 14.1.1 | Address Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14-2  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 14.1.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 14.1.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 14.1.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 14.1.5 | 8-Bit Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14-4  |

| 14.1.6 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 14.1.7 | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| 14.2   | Programming Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 14.2.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 14.2.2 | DRAM Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14-8  |

|        | 050TION 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|        | SECTION 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

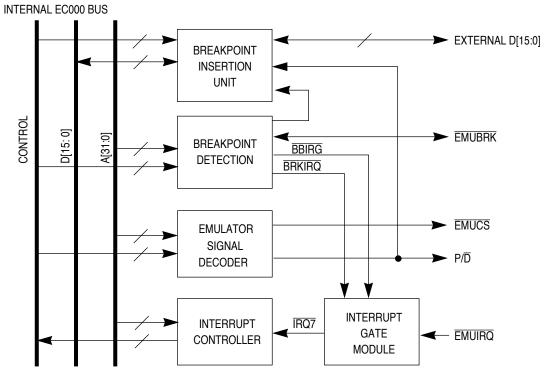

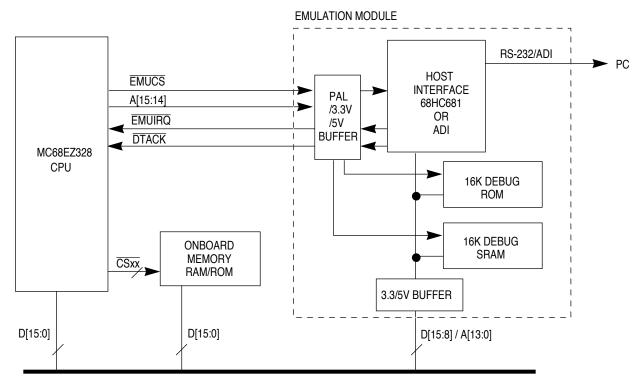

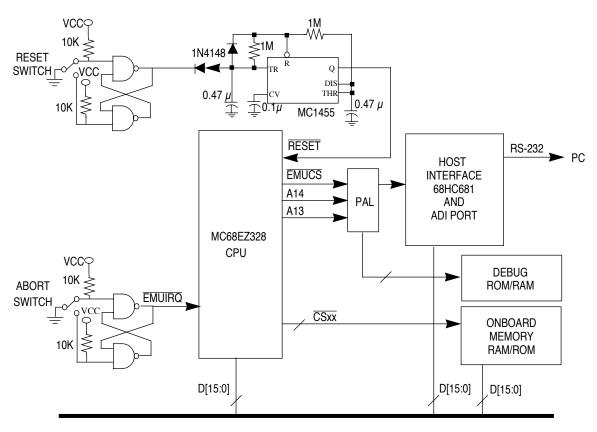

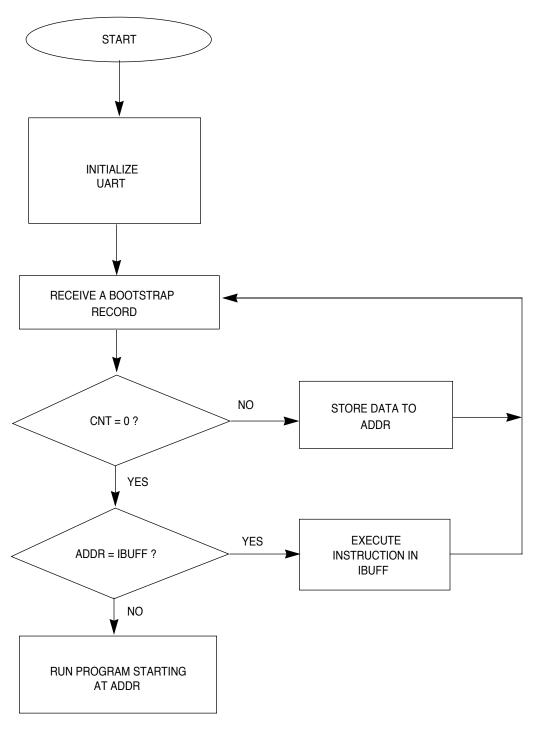

|        | IN-CIRCUIT EMULATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

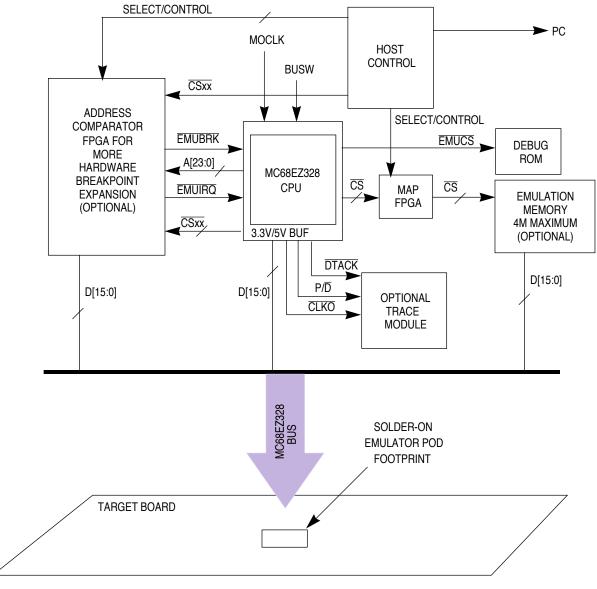

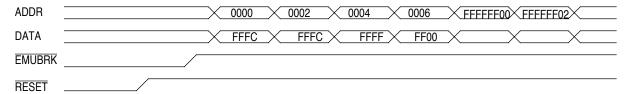

| 15.1   | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15-2  |

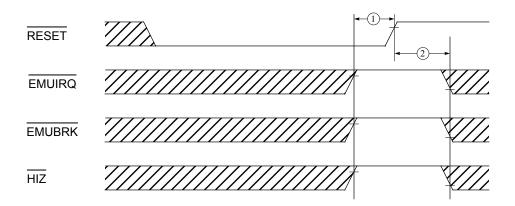

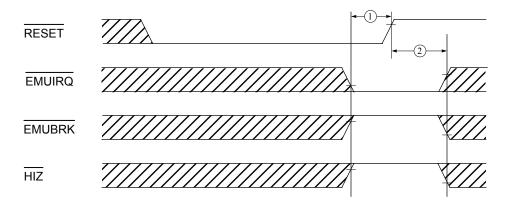

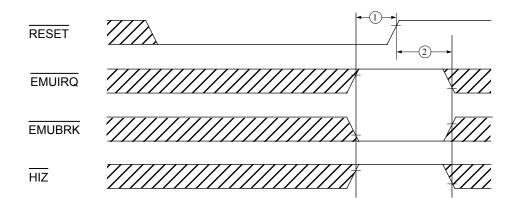

| 15.1.1 | Entering Emulation Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15-2  |

| 15.1.2 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 15.1.3 | Using the Signal Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15-3  |

| 15.1.4 | Using the Interrupt Gate Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15-3  |

| 15.1.5 | <b>5</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| 15.2   | Programming Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 15.2.1 | In-Circuit Emulation Module Address Compare/Mask Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| 15.2.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 15.2.3 | <b>3</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| 15.2.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 15.3   | Typical Design Programming Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| 15.3.1 | Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |