# SECTION 1 INTRODUCTION

The MC68328 DragonBall microprocessor is designed to save you time, power, cost, board space, pin count, and programming steps when designing your product. This functionality on a different microprocessor could require 20 separate components, each with 16-64 separate pins. Most of these components require interconnects, which may be duplicates. In fact, each of these connections could not only have a bad solder joint or misrouted trace, but may require another part to qualify, purchase, inventory, and maintain. These components take up valuable space on your PCB and they also consume more power. In addition, the signals between the CPU and a peripheral could be incompatible and may not run from the same clock, which could require time delays or other special design constraints.

All this combined makes the DragonBall the microprocessor of choice among many system designers. Its functionality and glue logic are all optimally connected, timed with the same clock, fully tested, and uniformly documented. Also, only the essential signals are brought out to the pins. The DragonBall's primary package consists of a surface-mount plastic TQFP designed to leave the smallest possible footprint on your board.

This manual will discuss the details of how to initialize, configure, and operate the DragonBall microprocessor. However, it assumes you have a basic knowledge of 68K architecture. If you are not familiar with 68K, you should get copies of the *M68000 User's Manual*, *M68000 Programmer's Reference Manual*, and *A Discussion of Interrupts for the MC68000* to use in conjunction with this manual. You can go to the Motorola website at http://www.motorola.com/pso to download these documents or you can contact your local sales office for printed versions.

# 1.1 FEATURES

The following list contains the main features of the DragonBall microprocessor:

- MC68EC000 Static Core Processor

- □ 100% Compatibility with MC68000 and MC68EC000 Processors

- □ 32-Bit Internal Address Bus

- 24-Bit External Address Bus with Optional 32-Bit Address Bus for a 4G Address Space

- □ 16-Bit On-Chip Data Bus for MC68EC000 Bus Operations

- □ Static Design Allows Processor Clock to Be Stopped to Save Power

- □ 2.7MIPS Performance Using a 16.67MHz Processor Clock

- Selectable Bus Sizing Support for Connecting to 8- and 16-Bit Devices

MOTOROLA

MC68328 USER'S MANUAL 11/6/97

## Introduction

- System Integration Module Supports Glueless System Design

- System Configuration and Programmable Address Mapping

- □ Memory Interface for SRAM, EPROM, and Flash Memory

- Sixteen Programmable Peripheral Chip-Selects with Wait-State Generation Logic

PCMCIA 1.0 Support

- Interrupt Controller with 13 Flexible Inputs

- Dependence of the Programmable Interrupt Vector Generator

- · Maximum of 77 Individually Programmable Parallel Port Signals

- Dual-Channel 16-Bit General-Purpose Counter/Timer

- Multimode Operation, Independent Capture and Compare Registers

- □ Automatic Interrupt Generation

- □ 60ns Resolution for a 16.67MHz System Clock

- □ Hardware and Software Watchdog Timers

- Separate Input and Output Pins for Capture and Compare.

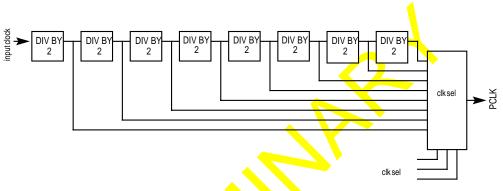

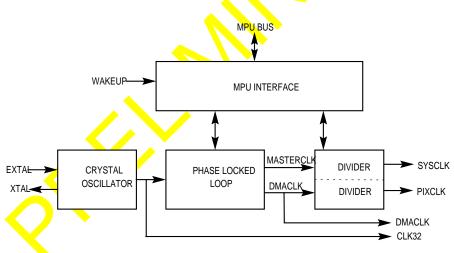

- Phase-Locked Loop and Power Management

- □ 3.3V Operation

- □ Fully Static HCMOS Technology

- Programmable Clock Synthesizer for Full Frequency Control

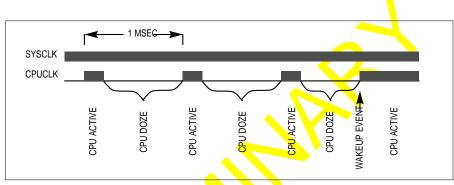

- Doze Mode Capability

- Low-Power Mode Control

- CPU Can Be Shut Down in Doze Mode

- Sleep Mode Can Be Entered By Shutting Down the Phase-Locked Loop (PLL)

- LCD Controller

- Software Programmable Screen Size to Drive Single Monochrome/STN Panels

- Directly Drives Common LCD Drivers and Modules

- Maximum of Four Grayscale Levels

- System Memory Can Be Used as Display Memory

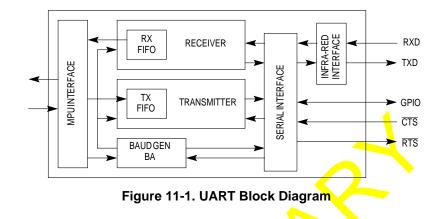

- UART

- □ < IrDA-Compliant Physical Layer Protocol Support

- □ 8-Byte Transmit and Receive FIFOs

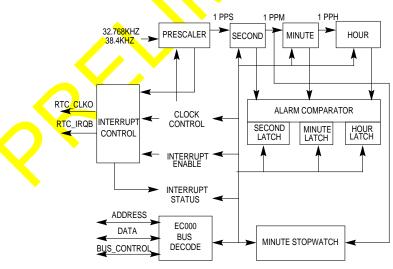

- Real-Time Clock

- 24-Hour Time

- Programmable Alarm

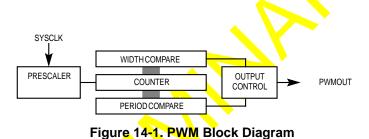

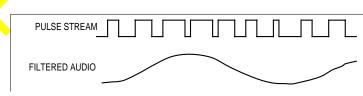

- Pulse-Width Modulation Output for Sound Generation

- □ Programmable Frame Rate

- □ 16-Bit Programmable

- □ Motor Control Support

- Two Serial Peripheral Interface Ports

## Introduction

- External POCSAG Decoder (Slave) Support

- Digitizer For A/D Input or FLEX Pager (Master) Support

- IEEE 1149.1 Boundary Scan Test Access Port (JTAG)

- Operation From DC To 16.67MHz (Processor Clock)

- Operating Voltage of  $3.3V\pm0.3V$

- Compact 144-Lead Thin-Quad-Flat-Pack (TQFP) Packaging

MOTOROLA

## MC68328 USER'S MANUAL 11/6/97

1-3

# 2 SIGNAL DESCRIPTIONS

# SECTION 2 SIGNALS

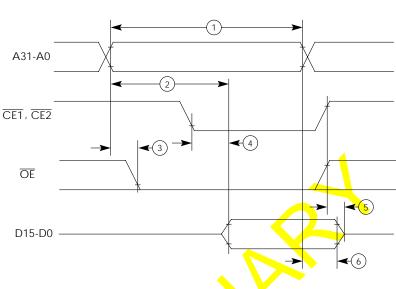

This section contains a description of the MC68328 DragonBall microprocessor signals, as well as the pin assignment of the 144-lead plastic thin-quad flat package (TQFP).

The DragonBall uses a standard M68000 bus for communication between both on-chip and external peripherals with optional address extension to A31. This single continuous bus exists both on the and off the chip. Read accesses made by the core to internal memory-mapped registers of the device are invisible on the external bus. Write accesses made by the core to internal or external memory mapped locations are visible on the external bus.

# 2.1 SIGNAL DESCRIPTIONS

The DragonBall signals are grouped as shown in Table 2-1.

| FUNCTIONAL GROUP                             | SIGNALS                                                                   | NUMBER OF PINS |

|----------------------------------------------|---------------------------------------------------------------------------|----------------|

| Clocks/PCIO                                  | XTAL, EXTAL, CLKO, PC0/MOCLK                                              | 4              |

|                                              | RESET, BBUSW                                                              | 2              |

| System Control/PCIO                          |                                                                           | -              |

| Address Bus, PAIO                            | PA7-PA0/A23-A16, A15–A0                                                   | 24             |

| Extended Address Bus/PFIO                    | PF7-PF0/A31-A24                                                           | 8              |

| Lower Data Bus/PBIO                          | PB7-PB0/D7-D0                                                             | 8              |

| Upper Data Bus                               | D15-D8                                                                    | 8              |

| Bus Control/PCIO                             | PC1/UDS. PC2/LDS, PC5/DTACK, AS, RW, OE, UWE, LWE                         | 8              |

| Interrupt Control/PDIO/Keyboard<br>Interrupt | PD7-PD0/KB7-KB0/INT7-INT0                                                 | 8              |

| Interrupt Control/PMIO                       | PM5/IRQ1, PM <u>4/IRQ</u> 2, PM3/IRQ3, PM2/IRQ6, PM6/<br>PENIRQ, PC4/IRQ7 | 6              |

| LCD Control                                  | LACD, LCLK, LLP, LFRM, LD0-LD3                                            | 8              |

| UART/PMIO/PGIO                               | PM7/GPIO, PG1/RXD, PG0/TXD, PM0/CTS, PM1/RTS                              | 5              |

| Timer/PGIO                                   | PG4/TIN2, PG <mark>6/TIN1, PG3/</mark> TOUT2, PG5/TOUT1                   | 4              |

| RTC/PGIO                                     | PG7/RTCO                                                                  | 1              |

| PWM/PGIO                                     | PG2/PWMO                                                                  | 1              |

| Chip Select                                  | CSA3–CSA0, CSB0-CSB3, CSC0-CSC3, CSD0-CSD3<br>PE7-PE0, PJ7-PJ0            | 16             |

| SPI Master                                   | PK0/SPMTXD0, PK1/SPMRXDI, PK2/ SPMCLKO                                    | 3              |

| SPI Slave                                    | PK3/SPSEN, PK4/SPSRXDI, PK5/SPSCLKI                                       | 3              |

| PCMCIA 1.0                                   | PC6/WE, PK6/CE2, PK7/CE1                                                  | 3              |

| In-circuit Testing                           | ICHIZ                                                                     | 1              |

| IEEE Testing                                 | TMS, JTAGRST, TDI, TDO, TCK                                               | 5              |

| Power                                        | V <sub>DD</sub> , PLLV <sub>DD</sub>                                      | 8              |

| Ground                                       | V <sub>SS</sub> , PLLV <sub>SS</sub>                                      | 10             |

Table 2-1. Signal Groups

**Note:** All pins except EXTAL support TTL levels. EXTAL, when used as an input clock, needs a CMOS level. To ensure proper low-power operation, all inputs should be driven CMOS level. Using a TTL level to drive those inputs could result in higher power consumption.

MC68328 USER'S MANUAL 11/6/97

# 2.1.1 Power Pins

The MC68328 processor has 20 power supply pins. Users should be careful to reduce noise, potential crosstalk, and RF radiation from the output drivers. Inputs may be +5 V or +3.3V when VDD = +3.3V or +5V respectively without damaging the device.

- VDD (7)—7 power pins

- VSS (9)—9 ground pins

- PLLVDD (1)—1 power pin for the PLL

- PLLVSS (1)—1 ground pin for the PLL

# 2.1.2 4. Clock Pins

# EXTAL—EXTERNAL CLOCK/CRYSTAL INPUT

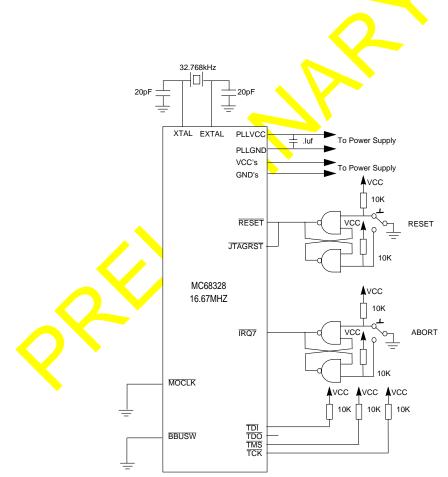

This input provides 3 clock generation options: (1) low frequency crystal, (2) low frequency external clock, and (3) high frequency external clock. While PCO/MOCLK is low, the on-chip phase-locked loop is enabled, creating the high-speed system clock from a low frequency reference. EXTAL may be used (with XTAL) to connect an external crystal to the on-chip oscillator and clock generator. If an external clock instead of a crystal is used, the clock source should be connected to EXTAL, and XTAL left unconnected. The internal PLL generates the system clock at 16.58 MHz from a 32.768 kHz or 38.4 kHz source. When an external clock is used, it must provide a CMOS level at this input frequency.

While PC0/MOCLK is high, the PLL is disabled and the system clock must be connected to the EXTAL pin. If the real-time clock is used, 32.768 kHz or 38.4 kHz must be driven into PG7/RTCO.

## XTAL—CRYSTAL OUTPUT

This output connects the on-chip oscillator output to an external crystal. If an external clock is used, XTAL should remain unconnected.

# CLKO—CLOCK OUT

This output clock signal is derived from the on-chip clock oscillator and is internally connected to the clock output of the internal PLL. This signal is provided for external reference. The output can be disabled to reduce power consumption.

## PC0/MOCLK—Clock Mode Select, Port C I/O

While this pin is high, the MC68328 processor is in the external clock mode and the on-chip PLL is disabled. The system clock must be driven into the EXTAL pin. While this pin is low, it enables the PLL. Either a 32.768 kHz or 38.4 kHz clock can be driven in to the EXTAL pin, or a crystal can be connected between EXTAL and XTAL to create an oscillator. PC0/MOCLK can be programmed as a general-purpose I/O while the internal PLL is enabled.

# 2.1.3 System Control Pins

## RESET

This active-low input signal causes the entire MC68328 processor (CPU and peripherals) to enter the reset state (cold reset). Users should drive this signal low for at least 100 msec at initial power-up to ensure that the crystal oscillator starts and stabilizes.

## **BBUSW—Boot Bus Width-Select**

This input defines the data bus width for the boot chip-select,  $\overline{CSA0}$ . BBUSW = 0 means the boot chip-select addresses an 8-bit memory space. BBUSW=1 means the boot memory space is 16-bits wide. Users can create a mixed 8/16 bit memory system by programming the memory space widths in the various chip-select control registers.

# 2.1.4 Address Bus Pins

These are the address lines driven by the 68EC000 core or by the LCD controller for panel refresh DMA. The chip-select module can decode the entire 4 Gbyte address map. In many applications, only the lower portion of the address lines will be used, reserving any unused address pins for parallel I/O functions.

# A15—A0

These address output lines are not multiplexed with any other I/O signals.

## PA7-PA0/A16-A23

These address lines are multiplexed with I/O port A. When programmed as I/O ports, they serve as general-purpose I/O ports; otherwise, they are output-only address signals. These signals default to address lines at reset where the address lines are all zeroes. Users should note that there may be contention if any logic "1" levels are driving these pins during or after reset.

## PF7-PF0/A31-A24

These bus pins are the extended address for 68EC000 core and are multiplexed with port F. In most systems, these lines are not used as addresses because most memory chips can be mapped into blocks of less than 16 Mbytes. These pins default to the port F I/O function after reset.

# 2.1.5 Data Bus Pins (D15–D0)

The flexible data bus interface design of the MC68328 processor allows users to program the lower byte of the data bus in an 8-bit-only system as general-purpose I/O signals.

## D15–D8

The upper byte of the data bus is not multiplexed with any other signals. In pure 8-bit systems, this is the data bus. In mixed 8-/16-bit systems, 8-bit memory blocks or peripherals should be connected to this bus.

MC68328 USER'S MANUAL 11/6/97

# PB7-PB0/D7-D0

This bus is the lower data byte or general-purpose I/O. In pure 8-bit systems, this bus can serve as a general-purpose I/O. The WDTH8 bit in the system control register (\$FFF000) should be set to one (1) by software before the port can be used. In 16-bit or mixed 8-/16-bit systems, these pins must function as the lower data byte.

# 2.1.6 Bus Control Pins

## **AS**—ADDRESS STROBE

This active-low output signal indicates that a valid address is present on the address bus. It is not asserted during LCD DMA accesses.

## R/W-READ/WRITE

This output signal defines the data bus transfer as a read or write cycle; read = 1; write = 0.

## PC1/UDS—UPPER DATA STROBE/PORT C I/O

This pin can be programmed as UDS or as a general-purpose I/O. When used as upper data strobe (UDS) output, this active-low signal is asserted when the internal EC000 core does a 16-bit word access or an even byte access. It is not asserted during LCD DMA accesses.

# PC2/LDS—LOWER DATA STROBE/PORT C I/O

This pin can be programmed as LDSor as a general-purpose I/O. When used as lower data strobe (LDS) output, this active-low signal is asserted when the internal EC000 core does a 16-bit word access or an odd byte access. It is not asserted during LCD DMA accesses.

## LWE, UWE — LOWER BYTE WRITE-ENABLE AND UPPER BYTE WRITE-ENABLE

On a write cycle to a 16-bit port, these active-low output signals indicate when the upper or lower 8 bits of the data bus contain valid data. In 8-bit mode or when the BSW bit in the chipselect register is 0, use only the upper write-enable (UWE) for write-enable control.

## PC4/IRQ7—LEVEL 7 INTERRUPT/PORT C I/O

When programmed as peripherals, this signal is an active-low input which, when asserted, will generate a level 7 interrupt to the CPU. When programmed as I/O, it becomes the PC 4 parallel I/O port.

# PC5/DTACK-DATA TRANSFER ACKNOWLEDGE, PC5

This pin can be programmed as parallel I/O PC5 or DTACK. While programmed as DTACK, this input signal indicates that the data transfer has been completed. DTACK is normally generated internally for all chip-selects. For systems that address spaces outside of the chip-select ranges, DTACK must be generated externally. PC5/DTACK must have an external pull-up resistor if programmed for the DTACK function.

## **OE**—OUTPUT-ENABLE

This active-low signal is asserted during a read cycle of the MC68328 processor, which enables the output of either ROM or SRAM. This signal also serves the PCMCIA 1.0 interface to indicate a read cycle.

MC68328 USER'S MANUAL 11/6/97

# 2.1.7 Interrupt Control Pins

# PD0-PD7/KB0-KB7/INT0-INT7—KEYBOARD AND GENERAL-PURPOSE INTERRUPT LINES

Users can program these signals as interrupt inputs or parallel I/O ports. For an interrupt port application,  $\overline{INTO}$ - $\overline{INT7}$  can be configured to perform keyboard interrupt functions. Keyboard interrupt pins  $\overline{KBO}$ - $\overline{KB7}$  are pulled high internally and connected to the rows of the keyboard matrix with the column driven low. When any one key of the row lines is pressed, an interrupt is generated to signal to the CPU to scan the keys. This feature, together with the pen interrupt, contributes a significant portion of the power management activities.

## PM6/PENIRQ—PEN INTERRUPT INPUT AND GENERAL-PURPOSE I/O

Users can program this pin as a general-purpose I/O PM6 or pen-interrupt input. When programmed as a pen-interrupt signal, this pin accepts an active low, level-triggered interrupt from the pen input device for a "pen-down" action.

# PM5-PM2/IRQ1, IRQ2, IRQ3, IRQ6

These pins can be programmed to either parallel I/O PM2-PM5 or interrupt input. When they function as interrupt inputs, they can be programmed to be edge or level triggered with either high or low polarity. IRQ6 generates a level 6 interrupt. IRQ3, IRQ2, and IRQ1 generate level 3, 2 and 1 interrupts respectively.

# 2.1.8 Chip Select Pins

## **CSA0**—BOOT CHIP-SELECT

CSA0 is the default chip-select after reset. It is set to 6 wait states and decodes all address ranges except internal register address space. It can be reprogrammed during the boot sequence to another address range and a different number of wait states.

# PE7-PE1/CSB3-CSB0, CSA3-CSA1-CHIP-SELECT GROUP A AND B

These pins comprise the remainder of the Group A and Group B chip-selects and are individually programmable. Pins that are not needed as chip-selects can be programmed as general-purpose I/Os. By default after reset, CSB3 is disabled and functions as a general-purpose input.

## PJ7-PJ0/CSD3-CSD0/CSC3-CSC0—CHIP-SELECT GROUP C AND D

These pins comprise the Group C and Group D chip-selects and are individually programmable. Pins that are not needed as chip-selects can be programmed as general-purpose I/Os.

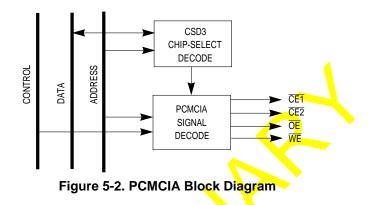

# 2.1.9 PCMCIA 1.0 PINS

## PC6/WE—WRITE ENABLE, PC6

This pin can be programmed as either PC6 parallel I/O or a write-enable signal for the PCMCIA 1.0 card interface. The MC68328 processor drives the active-low  $\overline{WE}$  signal to indicate a memory-write transfer to the PCMCIA 1.0 card. When programmed as I/O, it serves as PC6.

MC68328 USER'S MANUAL 11/6/97

## PK7-PK6/CE1-CE2

These pins can be programmed as either parallel I/O port K7-6 or the PCMCIA 1.0 chipenable signals. When programmed as the PCMCIA chip-enables,  $\overline{CE1}$  and  $\overline{CE2}$  are activelow, card-enable signals driven by the MC68328 processor;  $\overline{CE1}$  enables even bytes;  $\overline{CE2}$ enables odd bytes.  $\overline{CE1}$  and  $\overline{CE2}$  are decoded for assertion by  $\overline{CSD3}$ .

# 2.1.10 Master SPI Pins

## PK0/SPMTXD—MASTER SPI TRANSMIT DATA, PORT K 0

This pin is the master SPI shift register output. By default after reset, this pin becomes general-purpose input, PK0.

## PK1/SPMRXD—MASTER SPI RECEIVE DATA, PORT K 1

This pin is the input to the master SPI shift register. By default after reset, this pin becomes general-purpose input, PK1.

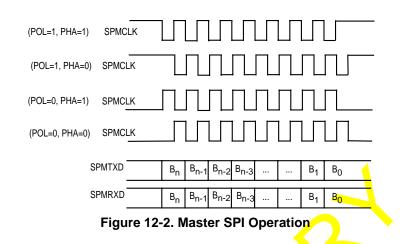

## PK2/SPMCLK—MASTER SPI CLOCK, PORT K 2

This pin is the clock output when the SPIM is enabled. In polarity = 0 mode, this signal is low while the SPIM is idle. In polarity = 1 mode, this signal is high during idle. By default after reset, this pin becomes general-purpose input, PK2.

# 2.1.11 Slave SPI Pins

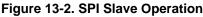

## PK5/SPSCLK—SLAVE SPI CLOCK, PORT K 5

This pin is the slave SPI clock output. By default after reset, this pin becomes generalpurpose input, PK5.

# PK4/SPSRXD-SLAVE SPI RECEIVE DATA, PORT K 4

This pin is the slave SPI shift register input. By default after reset, this pin becomes generalpurpose input, PK4.

# PK3/SPSSEN-SLAVE SPI ENABLE, PORT K 3

This pin is the slave SPI enable. While this signal is active, 8 clocks shift data into the slave SPI. This bit is programmable to be active high or low. By default after reset, it becomes general-purpose input, PK3.

# 2.1.12 UART Pins

## PG0/TXD—UART TRANSMIT DATA, PORT G 0

This pin is the transmitter serial output. While in normal mode, NRZ data is output. While in IrDA mode, a 3/16 bit-period pulse is output for each "zero" bit transmitted. For RS-232 applications, this pin must be connected to an RS-232 transmitter. For infrared applications, this pin can directly drive an IR LED or IR transceiver TXD signal. By default after reset, this pin becomes general-purpose input, PG0.

MC68328 USER'S MANUAL 11/6/97

## PG1/RXD—UART RECEIVE DATA, PORT G 1

This pin is the receiver serial input. While in normal operation, NRZ data is expected. While in infrared mode, a narrow pulse is expected for each "zero" bit received. An external IR transceiver RXD signal may be connected directly to this pin. RS-232 applications need an external RS-232 line-receiver to convert voltage levels. By default after reset, this pin becomes general-purpose input, PG1.

## PM0/CTS—CLEAR TO SEND, PORT M 0

This input controls the transmitter. Normally, the transmitter waits until this signal is active (low) before a character is transmitted. If the IGNORE CTS bit is set, the transmitter sends a character whenever a character is ready to transmit. This pin can then be used as a general-purpose input whose status is read in the CTS STATUS bit. This pin can post an interrupt on any transition of  $\overline{\text{CTS}}$ , if enabled. By default after reset, this pin becomes  $\overline{\text{CTS}}$ .

## PM1/RTS—REQUEST TO SEND, PORT M 1

This pin serves two purposes. Normally, the receiver indicates that it is ready to receive data by asserting this pin (low). This pin would be connected to the far-end transmitter's CTS pin. When the receiver detects a pending overrun, it negates this pin. For other applications, this pin can be a general-purpose output controlled by the bit in the receiver register. When it is programmed as parallel I/O, it becomes PM1. By default after reset, this pin becomes general-purpose input, PM1.

## PM7/GPIO—UART GENERAL PURPOSE I/O, PORT M 7

This pin provides several functions for the UART. It can provide a bit clock (input or output) and a master clock for the baud generator (input). By default after reset, this pin becomes UART GPIO.

## 2.1.13 Timer Pins

## PG6/TIN1—TIMER 1 INPUT, PORT G 6

This bidirectional pin can be programmed as a clock input that causes events to occur in timer/counter channel 1; either causing a clock to the event counter or providing a trigger to the timer value capture logic. By default after reset, this pin becomes general-purpose input, PG6.

## PG4/TIN2-TIMER 2 INPUT, PORT G 4

This bidirectional signal can be programmed as a clock input that causes events to occur in timer/counter channel 2; either causing a clock to the event counter or providing a trigger to the timer value capture logic. By default after reset, this pin becomes general-purpose input, PG4.

## PG5/TOUT1 —TIMER 1 OUTPUT, PORT G 5

This bidirectional signal can be programmed to toggle or generate a pulse of one system clock duration when timer/counter channel 1 reaches a reference value. By default after reset, this pin becomes general-purpose input, PG5.

MC68328 USER'S MANUAL 11/6/97

# PG3/TOUT2 —TIMER 2 OUTPUT, PORT G 3

This bidirectional signal can be programmed to toggle or generate a pulse of one system clock duration when timer/counter channel 2 reaches a reference value. By default after reset, this pin becomes general-purpose input, PG3.

# 2.1.14 PWM Pin

# PG2/PWMO—PULSE WIDTH MODULATOR OUTPUT, PORT G 2

This pin can serve as the PWM output signal. When it is PWMOUT, it produces synthesized sound, which can be connected to a filter and audio amplifier to generate melody and tone. By default after reset, this pin becomes general-purpose input, PG2.

# 2.1.15 Real-Time Clock Pins

# PG7/RTCO—REAL-TIME CLOCK OUTPUT/INPUT, PORT G7

While PC0/MOCLK is high, this pin is a dedicated input that provides the 32.768 kHz or 38.4 kHz clock to the real-time clock. While PC0/MOCLK is low, this pin can be programmed to output constant time tick pulses at the crystal frequency. By default after reset while PC0/MOCLK is low, this pin becomes general-purpose input, PG7.

# 2.1.16 LCD Controller Pins

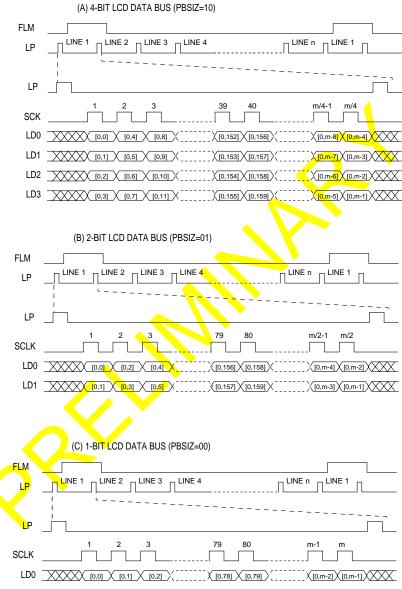

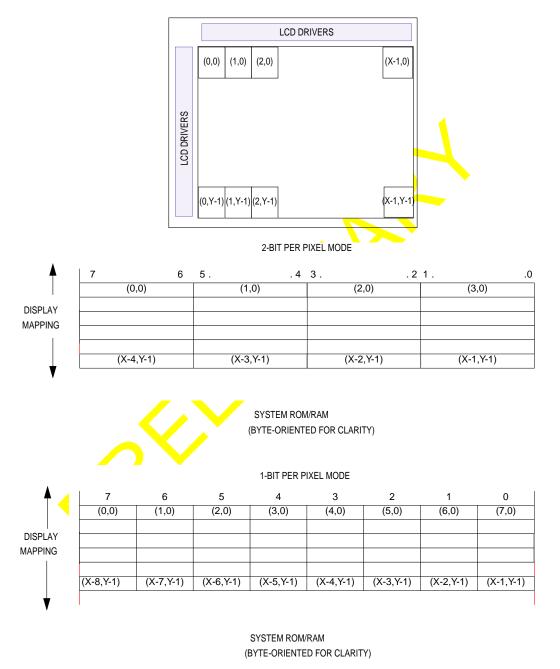

# LD3-LD0—LCD DATA BUS

This output bus transfers pixel data to the LCD panel for display. The pixel data is arranged to accommodate the programmable panel mode data width selection. Panel interfaces of one, two, or four bits are supported. Users can also program the output pixel data to be inverted for those LCD panels that require it.

The MC68328 LCD interface data bus uses LD0 to display pixel 0, 0. Some LCD panel manufacturers specify their LCD panel data bus where data bit 3 of the panel displays pixel 0,0. For these panels, the connections from the MC68328 LD bus to the LCD panel data bus are reversed in bit significance. Therefore, for these panels, connect LD0 of the MC68328 to LCD panel data bit 3, LD1 to LCD data 2, LD2 to LCD data 1, and LD3 to LCD data 0.

# LFLM-FIRST LINE MARKER

This signal indicates the start of a new display frame. LFLM becomes active after the first line pulse of the frame and remains active until the next line pulse, at which point it deasserts and remains inactive until the next frame. LFLM can be programmed to be an active-high or an active-low signal.

## LP—LINE PULSE

This signal latches a line of shifted data onto the LCD panel. It becomes active when a line of pixel data is clocked into LCD panels and remains asserted for 8 pixel clock periods. LP can be programmed to be either an active-high or an active-low signal.

# LCLK—SHIFT CLOCK

This is the clock output to which the output data to the LCD panel is synchronized. LCLK can be programmed to be inverted.

# LACD—ALTERNATE CRYSTAL DIRECTION

This output is toggled to alternate the crystal polarization on the panel and is used to protect the crystal from DC voltages. This signal can be programmed to toggle at a period from 1 to 16 frames.

# 2.1.17 JTAG Testing Pins

# TCK—TEST CLOCK

This pin provides a test clock input for boundary scan test logic defined by the IEEE1149.1 standard. If JTAG is not used or during normal operation, TCK should be connected to an extrnal pullup resistor.

# TMS—TEST MODE SELECT

This input controls test-mode operations for onboard test logic defined by the IEEE 1149.1 standard. If JTAG is not used, this pin should be connected to VDD or pulled up through an external pullup resistor.

# TDI-TEST DATA IN

This input is used for serial test instructions and test data for internal test logic defined by the IEEE 1149.1 standard. If JTAG is not used, this pin should be connected to VDD or pulled up through an external pullup resistor.

## TDO—TEST DATA OUT

This output is used for serial test instructions and test data for on-chip test logic defined by the IEEE 1149.1 standard. TDO may be left not connected or may drive the TDI pin of another device in a JTAG boundary scan chain.

## JTAGRST-JTAG RESET INPUT

This input is used for resetting the JTAG module for on-chip test logic defined by the IEEE 1149.1 standard for boundary scan. In normal operation, this pin should be connected to RESET.

# 2.1.18 In-Circuit Test Pin

## **ICHIZ—IN-CIRCUIT HIGH IMPEDANCE**

This input may be used as a means of isolating MC68328 signals during in-circuit testing. When  $\overline{\text{ICHIZ}}$  is asserted, all of the MC68328 signal pins are high impedance. When  $\overline{\text{HIZ}}$  is high, the MC68328 operates normally.  $\overline{\text{HIZ}}$  may also be asserted to accomodate in-circuit-test programming of external memory components such as FLASH memories.

Signals

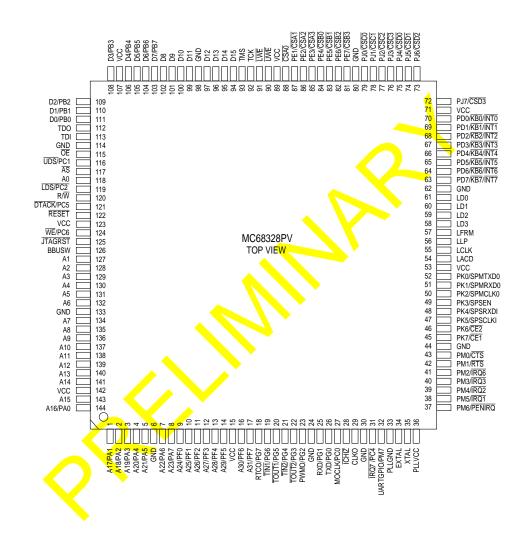

# 2.2 PIN ASSIGNMENT

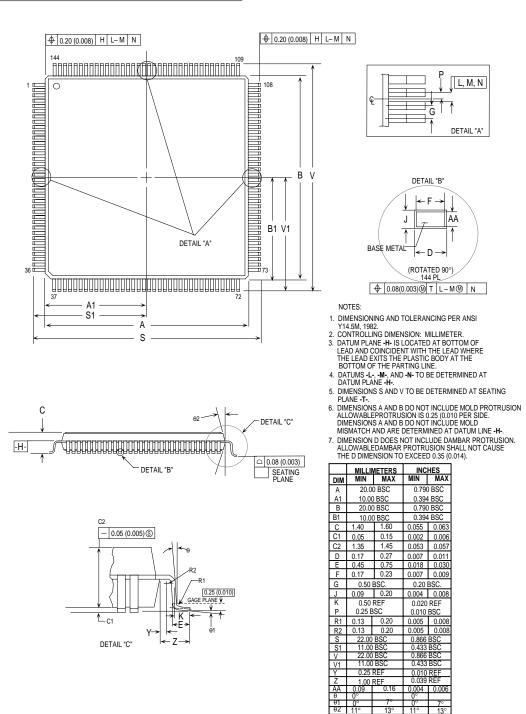

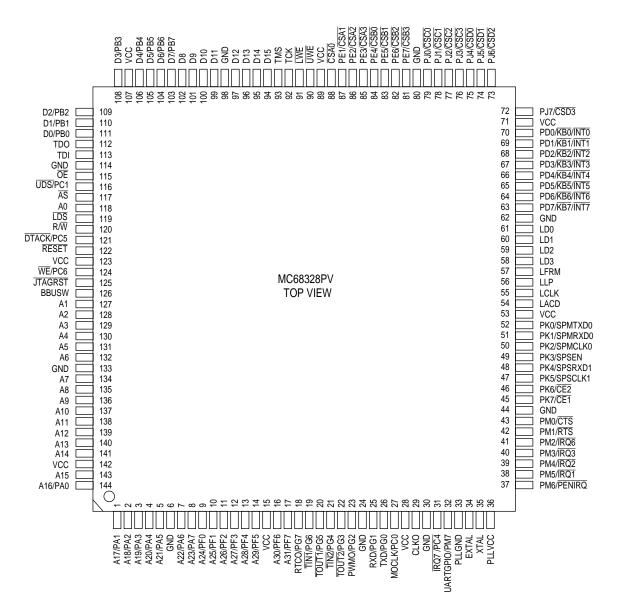

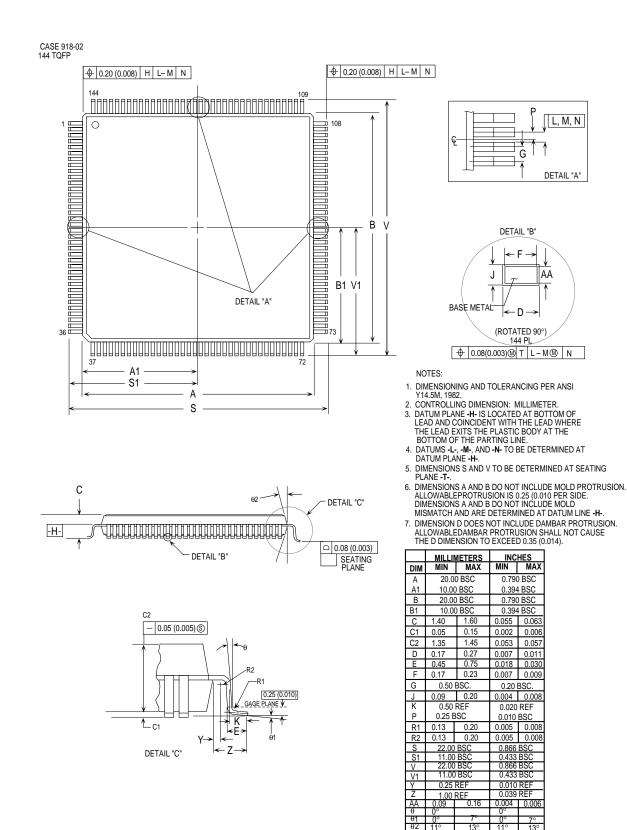

The MC68328 pin assignment is shown in Figure 2-1. Mechanical specifications for the 144-pin Thin Quad Flat Pack (TQFP) are shown in Figure 2-2.

Figure 2-1. Pin Assignment

MC68328 USER'S MANUAL 11/6/97

MOTOROLA

2 SIGNAL DESCRIPTIONS

2 SIGNAL DESCRIPTIONS

Figure 2-2. 144-Lead Plastic Thin-Quad Flat Package

MC68328 USER'S MANUAL 11/6/97

# SECTION 3 ARCHITECTURE

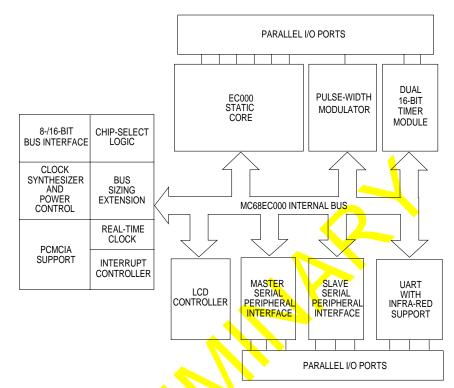

To improve total system throughput and reduce component count, board size, and cost of system implementation, the DragonBall combines a powerful MC68EC000 processor with intelligent peripheral modules and a typical system interface logic. The architecture of the DragonBall consists of the following blocks:

- EC000 core

- Chip-select logic and bus interface

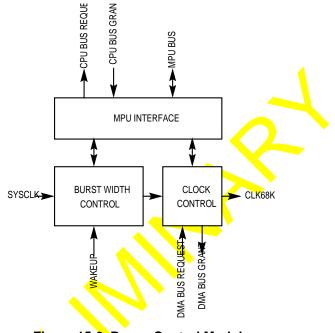

- Clock synthesizer and power management

- Interrupt controller

- Parallel general-purpose I/O ports

- Timers

- Low-power stop logic

- LCD controller

- UART

- · Real-time clock

- Pulse-width modulator

- Serial peripheral interface

This manual assumes you are familiar with 68K architecture. If you are not, get a copy of the *M68000 User's Manual* (part number M68000UM/AD) and *M68000 Programmer's Reference Manual* (part number M68000PM/AD) from your local Motorola sales office.

**3** ARCHITECTURE

# Figure 3-1. DragonBall Block Diagram

# **3.1 CORE**

The MC68EC000 core in the DragonBall is an updated implementation of the M68000 32-bit microprocessor architecture. The main features of the core are:

- Low power, static HCMOS implementation

- 32-bit address bus and 16-bit data bus

- 16 32-bit data and address registers

- 56 powerful instruction types that support high-level development languages

- 14 addressing modes and five main data types

- Seven priority levels for interrupt control

The core is completely code-compatible with other members of the M68000 families, which means it has access to a broad base of established real-time kernels, operating systems, languages, applications, and development tools.

MOTOROLA

3 ARCHITECTURE

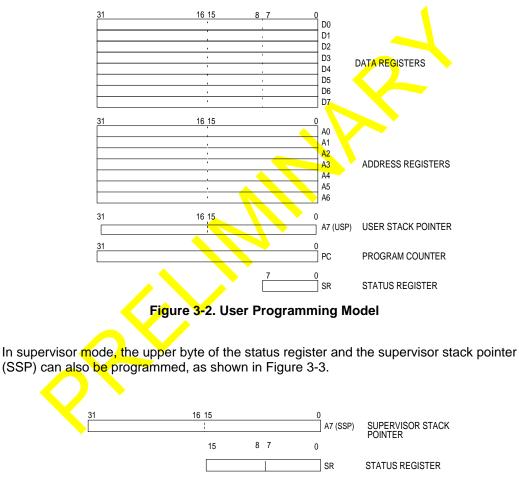

# 3.1.1 Core Programming Model

The core has 32-bit registers and a 32-bit program counter (see Figure 3-2). The first eight registers (D7–D0) are data registers that are used for byte (8-bit), word (16-bit), and long-word (32-bit) operations. When using the data registers to manipulate data, they affect the status register (SR). The next seven registers (A6–A0) and the user stack pointer (USP) can function as software stack pointers and base address registers. These registers can be used for word and long-word operations, but they do not affect the status register. The D7-D0 and A6-A0 registers can be used as index registers.

Figure 3-3. Supervisor Programming Model Supplement

The status register contains the interrupt mask with seven available levels, as well as an extend (X), negative (N), zero (Z), overflow (V), and carry (C) condition code. The T bit indicates when the processor is in trace mode and the S bit indicates when it is in supervisor or user mode.

```

MOTOROLA

```

MC68328 USER'S MANUAL 12/9/97

ARCHITECTURE

က

Architecture

# 3.1.2 Data and Address Mode Types

The core supports five types of data and six main types of address modes, as described in the following tables.

| DATA TYPES                  | ADDRESS MODE TYPES       |

|-----------------------------|--------------------------|

| Bits                        | Register direct          |

| Binary-coded decimal digits | Register indirect        |

| Bytes                       | Absolute                 |

| Words                       | Program counter relative |

| Long words                  | Immediate                |

|                             | Implied                  |

## Table 3-1. Address Modes

| ADDRESS MODE                                                                                                                                                                                           | SYNTAX                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Register direct address<br>Data register direct<br>Address register direct                                                                                                                             | Dn<br>An                                                                  |

| Absolute data address<br>Absolute short<br>Absolute long                                                                                                                                               | xxx.W<br>xxx.L                                                            |

| Program counter relative address<br>Relative with offset<br>Relative with index offset                                                                                                                 | d <sub>16</sub> (PC)<br>d <sub>8</sub> (PC, Xn)                           |

| Register indirect address register<br>Register indirect<br>Postincrement register indirect<br>Predecrement register indirect<br>Register indirect with offset<br>Indexed register indirect with offset | (An)<br>(An)+<br>–(An)<br>d <sub>16</sub> (An)<br>d <sub>8</sub> (An, Xn) |

| Immediate data address<br>Immediate<br>Quick immediate                                                                                                                                                 | #xxx<br>#1–#8                                                             |

| Implied address<br>Implied register                                                                                                                                                                    | SR/USP/SP/PC                                                              |

NOTE: Dn = Data Register An = Address Register Xn = Address or Data Register Used as Index Register SR = Status Register PC = Program Counter SP = Stack Pointer USP = User Stack Pointer C = Effective Address

- <> = Effective Address

d<sub>8</sub> = 8-Bit Offset (Displacement)

- d<sub>16</sub> = 16-Bit Offset (Displacement) #xxx = Immediate Data

MC68328 USER'S MANUAL 12/9/97

MOTOROLA

ω ARCHITECTURE

# 3.1.3 Instruction Set

The EC000 core instruction set supports high-level languages that facilitate programming. Almost every instruction operates on bytes, words, and long-words, and most of them can use any of the 14 address modes. By combining instruction types, data types, and address modes, you can have access to over 1,000 instructions. These instructions include signed and unsigned, multiply and divide, quick arithmetic operations, binary-coded decimal (BCD) arithmetic, and expanded operations (through traps).

| MNEMONIC    | DESCRIPTION                      | MNEMONIC     | DESCRIPTION                     |

|-------------|----------------------------------|--------------|---------------------------------|

| ABCD        | Add decimal with extend          | MOVEM        | Move multiple registers         |

| ADD         | Add                              | MOVEP        | Move peripheral data            |

| ADDA        | Add address                      | MOVEQ        | Move qu <mark>ic</mark> k       |

| ADDQ        | Add quick                        | MOVE from SR | Move from status register       |

| ADDI        | Add immediate                    | MOVE to SR   | Move to status register         |

| ADDX        | Add with extend                  | MOVE to CCR  | Move to condition codes         |

| AND         | Logical AND                      |              | Move user stack pointer         |

| ANDI        | AND immediate                    | MULS         | Signed multiply                 |

| ANDI to CCR | AND immediate to condition codes | MULU         | Unsigned multiply               |

| ANDI to SR  | AND immediate to status register | NBCD         | Negate decimal with extend      |

| ASL         | Arithmetic shift left            | NEG          | Negate                          |

| ASR         | Arithmetic shift right           | NEGX         | Negate with extend              |

| Bcc         | Branch conditionally             | NOP          | No operation                    |

| BCHG        | Bit test and change              | NOT          | Ones complement                 |

| BCLR        | Bit test and clear               | OR           | Logical OR                      |

| BRA         | Branch always                    | ORI          | OR immediate                    |

| BSET 🔸      | Bit test and set                 | ORI to CCR   | OR immediate to condition codes |

| BSR         | Branch to subroutine             | ORI to SR    | OR immediate to status register |

| BTST        | Bit test                         | PEA          | Push effective address          |

| СНК         | Check register against bounds    | RESET        | Reset external devices          |

| CLR         | Clear operand                    | ROL          | Rotate left without extend      |

| CMP         | Compare                          | ROR          | Rotate right without extend     |

| CMPA        | Compare address                  | ROXL         | Rotate left with extend         |

| СМРМ        | Compare memory                   | ROXR         | Rotate right with extend        |

| CMPI        | Compare immediate                | RTE          | Return from exception           |

| DBcc        | Test cond, decrement and branch  | RTR          | Return and restore              |

| DIVS        | Signed divide                    | RTS          | Return from subroutine          |

| DIVU        | Unsigned divide                  | SBCD         | Subtract decimal with extend    |

Table 3-2. Instruction Set

MOTOROLA

## MC68328 USER'S MANUAL 12/9/97

## Architecture

| MNEMONIC    | DESCRIPTION                               | MNEMONIC | DESCRIPTION               |

|-------------|-------------------------------------------|----------|---------------------------|

| EOR         | Exclusive OR                              | Scc      | Set conditional           |

| EORI        | Exclusive OR immediate                    | STOP     | Stop                      |

| EORI to CCR | Exclusive OR immediate to condition codes | SUB      | Subtract                  |

| EORI to SR  | Exclusive OR immediate to status register | SUBA     | Subtract address          |

| EXG         | Exchange registers                        | SUBI     | Subtract immediate        |

| EXT         | Sign extend                               | SUBQ     | Subtract quick            |

| JMP         | Jump                                      | SUBX     | Subtract with extend      |

| JSR         | Jump to subroutine                        | SWAP     | Swap data register halves |

| LEA         | Load effective address                    | TAS      | Test and set operand      |

| LINK        | Link stack                                | TRAP     | Тгар                      |

| LSL         | Logical shift left                        | TRAPV    | Trap on overflow          |

| LSR         | Logical shift right                       | TST      | Test                      |

| MOVE        | Move                                      | UNLK     | Unlink                    |

| MOVEA       | Move address                              |          |                           |

## Table 3-2. Instruction Set

# 3.2 CHIP-SELECT LOGIC AND BUS INTERFACE

The system control register (SCR) allows you to configure the system status and control logic, register double-mapping, bus error generation, and module control register protection on the DragonBall.

The DragonBall contains 16 programmable general-purpose chip-select signals. Each chip-select block allows you to choose whether the chip-select allows read-only or both read and write accesses, whether a DTACK is automatically generated for the chip-select, the number of wait states (from zero to six) until the DTACK will be generated, and an 8- or 16-bit data bus.

The external bus interface handles the transfer of information between the internal core and the memory, peripherals, or other processing elements in the external address space. It consists of a 16-bit M68000 data bus interface for internal-only devices and an 8- or 16-bit (or mixed) data bus interface to external devices.

MC68328 USER'S MANUAL 12/9/97

# 3.3 PLL CLOCK SYNTHESIZER AND POWER CONTROL

The clock synthesizer can operate with either an external crystal or an external oscillator using an internal phase-locked loop (PLL). An external clock can also be used to directly drive the clock signal at the operational frequency.

You can save power on the DragonBall by turning off peripherals that are not being used, reducing processor clock speed, or disabling the processor altogether. An interrupt at the interrupt controller logic that runs during low-power mode allows you to wake up from this mode. Programmable interrupt sources cause the system to wake up. On-chip peripherals can initiate a wake-up from doze mode and the external interrupts and real-time clock can wake up the core from sleep mode.

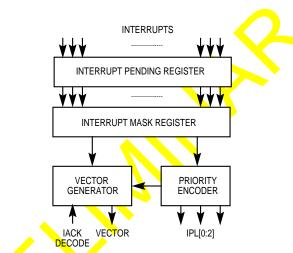

# 3.4 INTERRUPT CONTROLLER

The interrupt controller prioritizes internal and external interrupt requests and generates a vector number during the CPU interrupt-acknowledge cycle. Interrupt nesting is also provided so that an interrupt service routine of a lower priority interrupt may be suspended by a higher priority interrupt request. The on-chip interrupt controller has the following features:

- Prioritized interrupts

- Fully nested interrupt environment

- Programmable vector generation

- Unique vector number generated for each interrupt level

- Interrupt masking

- Wake-up interrupt masking

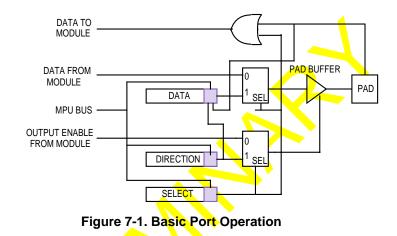

# 3.5 PARALLEL GENERAL-PURPOSE I/O PORTS

The DragonBall supports up to 77 general-purpose I/O ports that you can configure as general-purpose I/O pins or dedicated peripheral interface pins. Each pin can be independently programmed as a general-purpose I/O pin even when other pins related to that on-chip peripheral are used as dedicated pins. If all the pins for a particular peripheral are configured as general-purpose I/O, the peripheral will still operate normally.

# 3.6 TIMERS

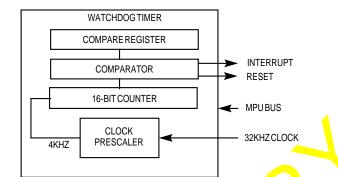

The software watchdog timer protects against system failures by providing a way for you to escape from unexpected input conditions, external events, or programming errors. Once started, the software watchdog timer must be cleared by software on a regular basis so that it never reaches its time-out value. When it does reach its time-out value, the watchdog timer assumes that a system failure has occurred and the software watchdog logic resets or interrupts the core.

MOTOROLA

**3** Architeoture

Architecture

# 3.7 LCD CONTROLLER

The LCD controller is used to display data on an LCD module. It fetches display data from memory and provides control signals, frame line pulse, clocks, and data to the LCD module. It supports monochrome STN LCD modules with a maximum of four grayscale levels with frame rate control. System RAM can be used as display memory and DMA frees the CPU from panel refresh responsibilities.

# 3.8 UART

The UART communicates with external devices with a standard asynchronous protocol at baud rates from 300bps to 115.2kpbs. The UART provides the pulses to directly drive standard IrDA transceivers.

# 3.9 REAL-TIME CLOCK

A The real-time clock provides time-of-day with one-second resolution. It uses the crystal (either 32.76 or 38.4kHz) as a clock source to keep proper time. It keeps time as long as power is applied to the chip, which can be in sleep or doze mode.

MC68328 USER'S MANUAL 12/9/97

# 3.10 PROGRAMMER'S MEMORY MAP

The memory map is a guide to all on-chip resources. Use the following table as a guide when configuring your chip. The base address used in the table is 0xFFFFF000 and 0xFFF000 from reset. If a double-mapped bit is cleared in the system control register, then the base address is 0xFFFFF000. Unpredictable results occur if you write to any 4K register space not documented in the table.

| ADDRESS    | NAME     | WIDTH | DESCRIPTION                           | RESET VALUE(HEX)   | PAGE # |

|------------|----------|-------|---------------------------------------|--------------------|--------|

| Base+0x000 | SCR      | 8     | System Control Register               | 0x <mark>0C</mark> | 4-2    |

| Base+0x004 | MRR      | 32    | Mask Revision Register                | (See note)         | System |

| Base+0x100 | GRPBASEA | 16    | Chip Select Group A Base Register     | 0x0000             | 5-4    |

| Base+0x102 | GRPBASEB | 16    | Chip Select Group B Base Register     | 0x0000             | 5-4    |

| Base+0x104 | GRPBASEC | 16    | Chip Select Group C Base Register     | 0x0000             | 5-4    |

| Base+0x106 | GRPBASED | 16    | Chip Select Group D Base Register     | 0x0000             | 5-4    |

| Base+0x108 | GRPMASKA | 16    | Chip Select Group A Mask Register     | 0x0000             | 5-5    |

| Base+0x10A | GRPMASKB | 16    | Chip Select Group B Mask Register     | 0x0000             | 5-5    |

| Base+0x10C | GRPMASKC | 16    | Chip Select Group C Mask Register     | 0x0000             | 5-5    |

| Base+0x10E | GRPMASKD | 16    | Chip Select Group D Mask Register     | 0x0000 5-3         |        |

| Base+0x110 | CSA0     | 32    | Group A Chip Select Option 0 Register | 0x00010006 5       |        |

| Base+0x114 | CSA1     | 32    | Group A Chip Select Option 1 Register | 0x00010006         | 5-6    |

| Base+0x118 | CSA2     | 32    | Group A Chip Select Option 2 Register | 0x00010006         |        |

| Base+0x11C | CSA3     | 32    | Group A Chip Select Option 3 Register | 0x00010006 5       |        |

| Base+0x120 | CSB0     | 32    | Group B Chip Select Option 0 Register | 0x00010006 5       |        |

| Base+0x124 | CSB1     | 32    | Group B Chip Select Option 1 Register | 0x00010006 5-6     |        |

| Base+0x128 | CSB2     | 32    | Group B Chip Select Option 2 Register | 0x00010006 5-6     |        |

| Base+0x12C | CSB3     | 32    | Group B Chip Select Option 3 Register | 0x00010006         | 5-6    |

| Base+0x130 | CSC0     | 32    | Group C Chip Select Option 0 Register | 0x00010006         | 5-6    |

| Base+0x134 | CSC1     | 32    | Group C Chip Select Option 1 Register | 0x00010006 5-0     |        |

| Base+0x138 | CSC2     | 32    | Group C Chip Select Option 2 Register | 0x00010006 5-6     |        |

| Base+0x13C | CSC3     | 32    | Group C Chip Select Option 3 Register | 0x00010006 5-6     |        |

| Base+0x140 | CSD0     | 32    | Group D Chip Select Option 0 Register | gister 0x00010006  |        |

| Base+0x144 | CSD1     | 32    | Group D Chip Select Option 1 Register | r 0x00010006 5-6   |        |

| Base+0x148 | CSD2     | 32    | Group D Chip Select Option 2 Register | 0x00010006         | 5-6    |

| Base+0x14C | CSD3     | 32    | Group D Chip Select Option 3 Register | 0x00010006         | 5-6    |

| Base+0x200 | PLLCR    | 16    | PLL Control Register                  | 0x2400             | PLL    |

| Base+0x202 | PLLFSR   | 16    | PLL Frequency Select Register         | 0x0123             | PLL    |

Table 3-3. Programmer's Memory Map

## MC68328 USER'S MANUAL 12/9/97

## Architecture

| ADDRESS    | NAME    | WIDTH | DESCRIPTION                      | RESET VALUE(HEX) PAGE |           |  |

|------------|---------|-------|----------------------------------|-----------------------|-----------|--|

| Base+0x207 | PCTLR   | 8     | Power Control Register           | 0x1F                  | PCTL      |  |

| Base+0x300 | IVR     | 8     | Interrupt Vector Register        | 0x00                  | 6-6       |  |

| Base+0x302 | ICR     | 16    | Interrupt Control Register       | 0x0000                | 6-6       |  |

| Base+0x304 | IMR     | 32    | Interrupt Mask Register          | 0x00FFFFFF            | 6-8       |  |

| Base+0x308 | IWR     | 32    | Interrupt Wakeup Enable Register | 0x00FFFFFF            | 6-11      |  |

| Base+0x30C | ISR     | 32    | Interrupt Status Register        | 0x0000000             | 6-14      |  |

| Base+0x310 | IPR     | 32    | Interrupt Pending Register       | -                     | 6-17      |  |

| Base+0x400 | PADIR   | 8     | Port A Direction Register        | 0x00                  | 7-7       |  |

| Base+0x401 | PADATA  | 8     | Port A Data Register             | 0x00                  | 7-7       |  |

| Base+0x403 | PASEL   | 8     | Port A Select Register           | 0x00                  | 7-7       |  |

| Base+0x408 | PBDIR   | 8     | Port B Direction Register        | 0x00                  | 7-8       |  |

| Base+0x409 | PBDATA  | 8     | Port B Data Register             | 0x00                  | 7-8       |  |

| Base+0x40B | PBSEL   | 8     | Port B Select Register           | 0x00 7                |           |  |

| Base+0x410 | PCDIR   | 8     | Port C Direction Register        | 0x00                  |           |  |

| Base+0x411 | PCDATA  | 8     | Port C Data Register             | 0x00                  | 7-9       |  |

| Base+0x413 | PCSEL   | 8     | Port C Select Register           | 0x00                  | 7-9       |  |

| Base+0x418 | PDDIR   | 8     | Port D Direction Register        | 0x00                  | 7-10      |  |

| Base+0x419 | PDDATA  | 8     | Port D Data Register             | 0x00                  |           |  |

| Base+0x41A | PDPUEN  | 8     | Port D Pullup Enable Register    | 0xFF 7·               |           |  |

| Base+0x41C | PDPOL   | 8     | Port D Polarity Register         | 0x00                  | 7-10      |  |

| Base+0x41D | PDIRQEN | 8     | Port D IRQ Enable Register       | 0x00                  | 7-10      |  |

| Base+0x41F |         | 8     | Port D IRQ Edge Register         | 0x00                  | 7-10      |  |

| Base+0x420 | PEDIR   | 8     | Port E Direction Register        | 0x00                  | 7-12      |  |

| Base+0x421 | PEDATA  | 8     | Port E Data Register             | 0x00                  | 7-12      |  |

| Base+0x422 | PEPUEN  | 8     | Port E Pullup Enable Register    | 0x80                  | 7-12      |  |

| Base+0x423 | PESEL   | 8     | Port E Select Register           | 0x80 7-               |           |  |

| Base+0x428 | PFDIR   | 8     | Port F Direction Register        | 0x00 7-13             |           |  |

| Base+0x429 | PFDATA  | 8     | Port F Data Register             | 0x00                  | 7-13      |  |

| Base+0x42A | PFPUEN  | 8     | Port F Pullup Enable Register    | 0xFF                  | 7-13      |  |

| Base+0x42B | PFSEL   | 8     | Port F Select Register           | 0xFF                  | 7-13      |  |

| Base+0x430 | PGDIR   | 8     | Port G Direction Register        | 0x00                  | 7-14      |  |

| Base+0x431 | PGDATA  | 8     | Port G Data Register             | 0x00                  | 7-14      |  |

| Base+0x432 | PGPUEN  | 8     | Port G Pullup Enable Register    | 0xFF                  | 7-14      |  |

| Base+0x433 | PGSEL   | 8     | Port G Select Register           | 0xFF                  | 7-14      |  |

| Base+0x438 | PJDIR   | 8     | Port J Direction Register        | 0x00                  | 0x00 7-16 |  |

# Table 3-3. Programmer's Memory Map (Continued)

3 ARCHITECTURE

MC68328 USER'S MANUAL 12/9/97

MOTOROLA

3-10

|                           | Table    | 5-5.1 | rogrammer's Memory Map (C                                    | ontinueu)          |        |  |

|---------------------------|----------|-------|--------------------------------------------------------------|--------------------|--------|--|

| ADDRESS                   | NAME     | WIDTH | DESCRIPTION                                                  | RESET VALUE(HEX)   | PAGE # |  |

| Base+0x439                | PJDATA   | 8     | Port J Data Register                                         | 0x00               | 7-16   |  |

| Base+0x43B                | PJSEL    | 8     | Port J Select Register                                       | 0x00               | 7-16   |  |

| Base+0x440                | PKDIR    | 8     | Port K Direction Register                                    | 0x00               | 7-17   |  |

| Base+0x441                | PKDATA   | 8     | Port K Data Register                                         | 0x00               | 7-17   |  |

| Base+0x442                | PKPUEN   | 8     | Port K Pullup Enable Register                                | 0x3F               | 7-17   |  |

| Base+0x443                | PKSEL    | 8     | Port K Select Register                                       | 0x3F               | 7-17   |  |

| Base+0x448                | PMDIR    | 8     | Port M Direction Register                                    | 0x <mark>00</mark> | 7-18   |  |

| Base+0x449                | PMDATA   | 8     | Port M Data Register                                         | 0x00               | 7-18   |  |

| Base+0x44A                | PMPUEN   | 8     | Port M Pullup Enable Register                                | 0xFF               | 7-18   |  |

| Base+0x44B                | PMSEL    | 8     | Port M Select Register                                       | 0x02               | 7-18   |  |

| Base+0x500                | PWMC     | 16    | PWM Control Register                                         | 0x0000             | PWM    |  |

| Base+0x502                | PWMP     | 16    | PWM Period Register                                          | 0x0000 PWI         |        |  |

| Base+0x504                | PWMW     | 16    | PWM Width Register                                           | 0x0000 P           |        |  |

| Base+0x506                | PWMCNT   | 16    | PWM Count <mark>er Register</mark>                           | 0x0000 P           |        |  |

| Base+0x600                | TCTL1    | 16    | Timer Unit 1 Control Register                                | 0x0000             | 10-4   |  |

| Base+0x602                | TPRER1   | 16    | Timer Un <mark>it 1</mark> Pres <mark>cal</mark> ar Register | 0x0000             | 10-5   |  |

| Base+0x604                | TCMP1    | 16    | Timer Unit 1 Compare Register                                | 0xFFFF 1           |        |  |

| Base+0x606                | TCR1     | 16    | Timer Unit 1 Capture Register                                | 0x0000             | 10-6   |  |

| Base+0x608                | TCN1     | 16    | Timer Unit 1 Counter Register                                | 0x0000 10          |        |  |

| Base+0x60A                | TSTAT1   | 16    | Timer Unit 1 Status Register                                 | 0x0000 10-         |        |  |

| Base+0x60C                | TCTL2    | 16    | Timer Unit 2 Control Register                                | 0x0000 10          |        |  |

| Base+0x60E                | TPREP2   | 16    | Timer Unit 2 Prescaler Register                              | 0x0000 10          |        |  |

| Base+0x610                | TCMP2    | 16    | Timer Unit 2 Compare Register                                | 0xFFFF             | 10-6   |  |

| Base+0x612                | TCR2     | 16    | Timer Unit 2 Capture Register                                | 0x0000 10-         |        |  |

| Base+0x614                | TCN2     | 16    | Timer Unit 2 Counter Register                                | 0x0000 10-         |        |  |

| Base+0x <mark>6</mark> 16 | TSTAT2   | 16    | Timer Unit 2 Status Register                                 | 0x0000 10-         |        |  |

| Base+0x618                | WCSR     | 16    | Watchdog Control and Status Register                         | 0x0001 10-5        |        |  |

| Base+0x61A                | WRR      | 16    | Watchdog Compare Register                                    | 0xFFFF 10-         |        |  |

| Base+0x61C                | WCN      | 16    | Watchdog Counter Register                                    | 0x0000 10-8        |        |  |

| Base+0x700                | SPISR    | 16    | SPIS Register                                                | 0x0000 S           |        |  |

| Base+0x800                | SPIMDATA | 16    | SPIM Data Register                                           | 0x0000 SPIN        |        |  |

| Base+0x802                | SPIMCONT | 16    | SPIM Control/Status Register                                 | 0x0000             | SPIM   |  |

| Base+0x900                | USTCNT   | 16    | UART Status/Control Register                                 | 0x0000             | 11-7   |  |

| Base+0x902                | UBAUD    | 16    | UART Baud Control Register                                   | 0x003F             | 11-10  |  |

| Base+0x904                | URX      | 16    | UART RX Register                                             | 0x0000 11-12       |        |  |

Table 3-3. Programmer's Memory Map (Continued)

MOTOROLA

## MC68328 USER'S MANUAL 12/9/97

3-11

**3** ARCHITEGTURE

## Architecture

| ADDRESS    | NAME   | WIDTH | DESCRIPTION RESET VALUE(HEX)                  |                                           |       |  |

|------------|--------|-------|-----------------------------------------------|-------------------------------------------|-------|--|

| Base+0x906 | UTX    | 16    | UART TX Register                              | 0x0000                                    | 11-13 |  |

| Base+0x908 | UMISC  | 16    | UART Misc Register                            | 0x0000                                    | 11-15 |  |

| Base+0xA00 | LSSA   | 32    | LCD Screen Starting Address Register          | 0x0000000                                 | 8-15  |  |

| Base+0xA05 | LVPW   | 8     | LCD Virtual Page Width Register               | 0xFF                                      | 8-15  |  |

| Base+0xA08 | LXMAX  | 16    | LCD Screen Width Register                     | 0x03FF                                    | 8-16  |  |

| Base+0xA0A | LYMAX  | 16    | LCD Screen Height Register                    | 0x01FF                                    | 8-16  |  |

| Base+0xA18 | LCXP   | 16    | LCD Cursor X Position Register                | 0x0 <mark>0</mark> 00                     | 8-17  |  |

| Base+0xA1A | LCYP   | 16    | LCD Cursor Y Position Register                | <b>0x000</b> 0                            | 8-17  |  |

| Base+0xA1C | LCWCH  | 16    | LCD Cursor Width & Height Register            | 0x0101                                    | 8-18  |  |

| Base+0xA1F | LBLKC  | 8     | LCD Blink Control Register                    | 0x7F                                      | 8-18  |  |

| Base+0xA20 | LPICF  | 8     | LCD Panel Interface Configuration<br>Register | D Panel Interface Configuration 0x00 0x00 |       |  |

| Base+0xA21 | LPOLCF | 8     | LCD Polarity Configuration Register 0x00      |                                           | 8-20  |  |

| Base+0xA23 | LACDRC | 8     | ACD (M) Rate Control Register                 | D (M) Rate Control Register 0x00          |       |  |

| Base+0xA25 | LPXCD  | 8     | LCD Pixel Clock Divider Register              | 0x00                                      | 8-21  |  |

| Base+0xA27 | LCKCON | 8     | LCD Clocking Control Register                 | 0x40                                      |       |  |

| Base+0xA29 | LLBAR  | 8     | LCD Last Buffer Address Register              | 0x3E                                      | 8-23  |  |

| Base+0xA2B | LOTCR  | 8     | LCD Octet Terminal Count Register             | 0x3F                                      | 8-23  |  |

| Base+0xA2D | LPOSR  | 8     | LCD Panning Offset Register                   | 0x00                                      | 8-24  |  |

| Base+0xA31 | LFRCM  | 8     | LCD Frame-Rate Modulation Control<br>Register |                                           |       |  |

| Base+0xA32 | LGPMR  | 16    | LCD Gray Palette Mapping Register             | ing Register 0x1073                       |       |  |

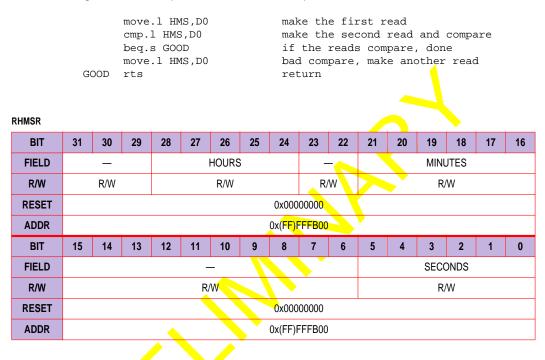

| Base+0xB00 | HMSR   | 32    | RTC Hours Minutes Seconds Register            | egister 0xXXXXXXX                         |       |  |

| Base+0xB04 | ALARM  | 32    | RTC Alarm Register 0x00000000                 |                                           | 9-4   |  |

| Base+0xB0C | СТЬ    | 8     | RTC Control Register 0xXX                     |                                           | 9-5   |  |

| Base+0xB0E | ISR    | 8     | RTC Interrupt Status Register                 | 0x00                                      | 9-5   |  |

| Base+0xB10 | IENR   | 8     | RTC Interrupt Enable Register                 | 0x00                                      | 9-7   |  |

| Base+0xB12 | STPWCH | 8     | RTC Stopwatch Register 0x00                   |                                           | 9-8   |  |

# Table 3-3. Programmer's Memory Map (Continued)

MC68328 USER'S MANUAL 12/9/97

# SECTION 4 SYSTEM CONTROL

The DragonBall microprocessor contains a system control register that enables the system software to customize the following functions:

- Access permission from the internal peripheral registers

- · Address space of the internal peripheral registers

- · Bus timeout control and status (bus-error generator)

# 4.1 OPERATION

The on-chip resources use a reserved 4,096-byte block of address space for their registers. This block is double-mapped to two locations—0xFFFEF000 (24-bit) and 0xFFF000 (32-bit) —at reset. The DMAP bit in the system control register disables double-mapping in a 32-bit system. If you clear this bit, the on-chip peripheral registers appear only at the top of the 4G address range starting at 0xFFFF000.

The system control register allows you to control system operation functions like bus interface and hardware watchdog protection. It contains status bits that allow exception handler code to investigate the cause of exceptions and resets. The hardware watchdog (bus timeout monitor) and the software watchdog timer provide system protection. The hardware watchdog provides a bus monitor that causes a bus error when a bus cycle is not terminated by the DTACK signal before 128 clock cycles have elapsed.

The bus error timeout logic consists of a watchdog counter that, when enabled, begins to count clock cycles as the  $\overline{AS}$  pin is asserted for internal or external bus accesses. The negation of  $\overline{AS}$  normally terminates the count, but if the count reaches terminal count before  $\overline{AS}$  is negated, BERR is asserted until  $\overline{AS}$  is negated. The bus error timeout logic uses one control bit and one status bit in the system control register. The BETO bit in the system control register is set after a bus timeout, which could be caused by a write-protect violation.

The software watchdog timer resets the DragonBall if enabled and not cleared or disabled before reaching terminal count. The software watchdog timer is enabled at reset. For information about timer operation, see **Section 8.3 Software Watchdog Timer**.

System Control

# 4.1.1 System Control Register

The 8-bit read/write system control register (SCR) resides at 0xFFF000 or 0xFFFF000 after reset. The SCR cannot be accessed in user data space if the SO bit is set to 1. Writing a 1 to the status bits in this register clears them, but writing a 0 has no effect.

## SCR

| BIT   | 7            | 6   | 5   | 4     | 3   | 2    | 1        | 0     |  |

|-------|--------------|-----|-----|-------|-----|------|----------|-------|--|

| FIELD | BETO         | WPV | PRV | BETEN | SO  | DMAP | RESERVED | WDTHB |  |

| R/W   | R/W          | R/W | R/W | R/W   | R/W | R/W  | R/W      | R/W   |  |

| RESET | 0x0C         |     |     |       |     |      |          |       |  |

| ADDR  | 0x(FF)FFF000 |     |     |       |     |      |          |       |  |

## BETO—Bus Error Time-Out

This status bit indicates whether or not a bus error timer time-out has occurred. When a bus cycle is not terminated by the DTACK signal after 128 clock cycles have elapsed, the BETO bit is set. However, the BETEN bit must be set for a bus error timeout to occur. This bit is cleared by writing a 1 (writing a 0 has no effect).

- 0 = A bus error timer time-out did not occur.

- 1 = A bus error timer time-out occurs because an undecoded address space has been accessed or because a write-protect or privilege violation has occurred.

## WPV—Write-Protect Violation

This status bit indicates that a write-protect violation has occurred. If a write-protect violation occurs and the BETEN bit is not set, the cycle will not terminate. The BETEN bit must be set for a bus error exception to occur during a write-protect violation. This bit is cleared by writing a 1 (writing a 0 has no effect).

- 0 = A write-protect violation did not occur.

- 1 = A write-protect violation has occurred.

## PRV—Privilege Violation

This status bit indicates that If a privilege violation occurs and the BETEN bit is not set, the cycle will not terminate. The BETEN bit must be set for a bus error exception to occur during a privilege violation. This bit is cleared by writing a 1 (writing a 0 has no effect).

- 0 = A privilege violation did not occur.

- 1 = A privilege violation has occurred.

BETEN—Bus-Error Timeout Enable

This control bit enables the bus error timer.

- 0 = Disable the bus error timer.

- 1 = Enable the bus error timer.

MC68328 USER'S MANUAL 12/9/97

SO—Supervisor Only

This control bit limits on-chip registers to supervisor accesses only.

- 0 = User and supervisor mode.

- 1 = Supervisor-only mode.

DMAP—Double Map

This control bit controls the double-mapping function.

- 0 = The on-chip registers are mapped at 0xFFFFF000–0xFFFFFFF.

- 1 = The on-chip registers are mapped at 0xxxFFF000–0xxxFFFFFF.

# Bit 1—Reserved

This bit is reserved and reads 0.

WDTH8—8-Bit Width Select

This control bit allows the D[7:0] pins to be used for port B input/output.

0 = Not an 8-bit system.

1 = 8-bit system.

## MC68328 USER'S MANUAL 12/9/97

System Control

4 SYSTEM CONTROL

4-4

MC68328 USER'S MANUAL 12/9/97

7,

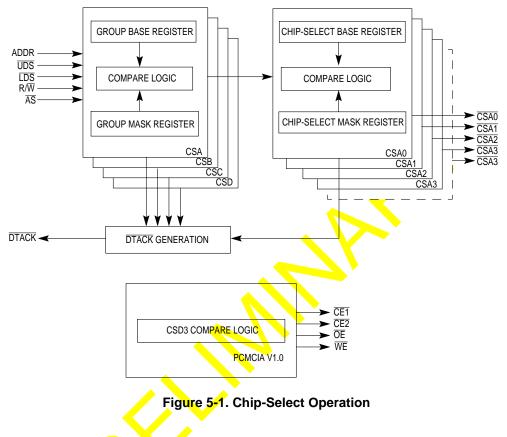

# SECTION 5 CHIP-SELECT LOGIC

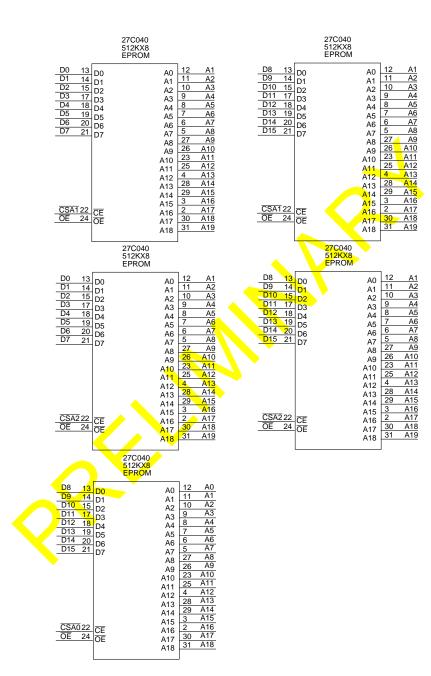

The DragonBall microprocessor contains 16 general-purpose, programmable, chip-select signals, which are arranged in four groups of four. Among them, there are two special-purpose chip-select signals—CSA0 and CSD3. The CSA0 signal is special in that it is also a boot device chip-select. From reset, all the addresses are mapped to CSA0 until group-base address A is programmed and the V bit is set. From that point on, CSA0 does not decode globally and it is only asserted when decoded from the programming information in the group-base address register, group-base address mask register, chip-select base register, and chip-select option register. The CSD3 signal is asserted, the PCMCIA control signals are asserted. For each memory area, you can define an internally generated cycle-termination signal, called DTACK, with a programmable number of wait states. This feature saves board space that would otherwise be used for cycle-termination logic.

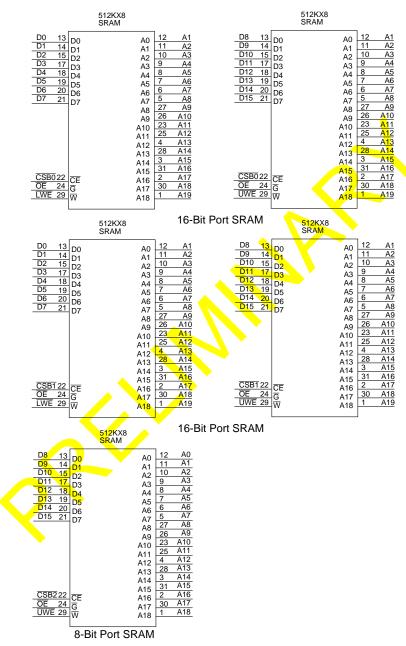

The 16 general-purpose chip-selects allow different classes of devices and memory to be used in a system without external decode or wait-state generation logic. A typical configuration would be an 8-bit EPROM, a fast 16-bit SRAM, four simple I/O peripherals, and a nonvolatile flash memory. See Section 16 Applications and Design Examples for more information.

# 5.1 CHIP-SELECT OPERATION

A chip-select output signal is asserted when an address is matched and after the  $\overline{AS}$  signal goes low. The base address and address mask registers are used in the compare logic to generate an address match. The byte size of the matching block must be a power of 2 and the base address must be an integer multiple of this size. Therefore, an 8K block size must begin on an 8K boundary and a 64K block size can only begin on a 64K boundary. Each chip-select is programmable and the registers have read/write capability so that the programmed values can be read back.

You can choose whether the chip-select allows read-only or read/write accesses, whether a DTACK signal is automatically generated for the chip-select, the number of wait states (from zero to six), and data bus size selection.

Note: The chip-select logic does not allow an address match during interrupt acknowledge (Function Code 7) cycles.

MC68328 USER'S MANUAL 12/9/97

# 5.1.1 Programmable Data Bus Size

Each chip-select can be configured to address an 8- or 16-bit space. You can mix 16- and 8-bit contiguous address memory devices on a 16-bit data bus system. If the core performs a 16-bit data transfer in an 8-bit memory space, then two 8-bit cycles will occur. However, the address and data strobes remain asserted until the end of the second 8-bit cycle. In this case, only the external core data bus upper byte (D[15:8]) is used and the least-significant bit of address (A0) increments automatically from one to the next. A0 should be ignored in 16-bit data-bus cycles even if only the upper or lower byte is being read or written. For an external peripheral that only needs an 8-bit data bus interface and does not require contiguous address locations (unused bytes on empty addresses), use a chip-select configured to a 16-bit data bus width and connect to the D[7:0] pins. This balances the load of the two data bus halves in an 8-bit system. The internal data bus is16 bits wide. All internal registers can be read or written in one zero wait-state cycle.

Each chip-select defaults to a 16-bit data bus width. The BUSW field in the chip-select option registers enable 16- and 8-bit data bus widths for each of the 16 chip-select ranges. You can select the initial bus width for the boot chip-select by placing a logic 0 or 1 on the BBUSW pin at reset to specify the width of the data bus. This allows a boot EPROM of the data bus width to be used in any given system. All external accesses that do not match one of the chip-select address ranges are assumed to be a 16-bit device. That is just one access performed for a 16-bit transfer. It can also be a 8-bit port accessed every other byte.

The boot chip-select is initialized from reset to assert in response to any address except the on-chip register space (0xXXFFF000 to 0xXXFFFFFF). This ensures that a chip-select to the boot ROM or EPROM will fetch the reset vector and execute the initialization code, which should set up the chip-select ranges.

A logic 0 on the BBUSW pin makes the boot device's data bus 8 bits wide and a logic 1 makes it 16 bits wide. At reset, the data bus port size for  $\overline{CSA0}$  and the data width of the boot ROM device are determined by the state of the BBUSW pin. The other chip-selects are initialized to be nonvalid, so they will not assert until they are programmed and the V bit is set.

Note: If the group address and chip-select registers are programmed to overlap, the CSx signals will overlap too. Unused chip-selects must be programmed to 0 wait states and 16 bits wide. Map them to dummy space if necessary. When you are configuring the chip-select signals, the core can be set to write to a read-only location. This causes the CS and DTACK signals to not be asserted and the BERR signal to be asserted if a bus error timer is enabled.

**Chip-Select Logic**

# 5.2 PROGRAMMING MODEL

The chip-select module of the DragonBall microprocessor contains registers that you can use to control external devices, such as memory. Chip-selects do not operate until the register in a particular group of devices is initialized and the V bit is set in the corresponding group-base address register. The only exception is the CSA0 signal, which is the boot device chip-select.

# 5.2.1 Group Base Address Registers

There are four 16-bit group base address registers (GRPBASEA–GRPBASED) in the chip-select module (one for each chip-select group). The group base address registers and the group mask registers decode the upper address bits and the chip-select option registers decode the lower address bits. There are four chip-selects in each group. For example, in group A the chip-selects are CSA0, CSA1, CSA2, and CSA3.

## GRPBASEA-GRPBASED

| BIT   | 15                          | 14    | 13    | 12    | 11    | 10    | 9     | 8     | 7     | 6     | 5     | 4     | 3          | 2 | 1 | 0 |

|-------|-----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------------|---|---|---|

| FIELD | GBA31                       | GBA30 | GBA29 | GBA28 | GBA27 | GBA26 | GBA25 | GBA24 | GBA23 | GBA22 | GBA21 | GBA20 | RESERVED V |   |   | v |

| R/W   | R/W                         | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | — R/W      |   |   |   |

| RESET | T 0x0000                    |       |       |       |       |       |       |       |       |       |       |       |            |   |   |   |

| ADDR  | 0x(PF)FFF100, 102, 104, 106 |       |       |       |       |       |       |       |       |       |       |       |            |   |   |   |

# GBA—Group Base Address 31–20

This bit selects the starting address for the group address range. The corresponding bits in the group base mask register define the block size for the group. This field is compared to the address on the address bus to determine if the group is decoded.

Bits 1–3—Reserved These bits are reserved.

## V—Valid

This bit controls whether or not the contents of its base address register and address mask register pair are valid. The programmed chip-selects do not assert until this bit is set. A reset clears this bit in each base address register.

- 0 = Content is not valid.

- 1 = Content is valid.

# 5.2.2 Group Base Address Mask Registers

The group base address mask registers (GRPMASKA–GRPMASKD) define the address comparison range for a group of devices. When the bits in this register are set to 1 the bits in the corresponding address lines (A[31:20]) compare true ("don't care").

| GRPMASKA-GRPMASKD |

|-------------------|

|-------------------|

| BIT   | 15     | 14                          | 13    | 12    | 11    | 10    | 9     | 8     | 7     | 6     | 5     | 4     | 3        | 2 | 1 | 0 |

|-------|--------|-----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------|---|---|---|

| FIELD | GMA31  | GMA30                       | GMA29 | GMA28 | GMA27 | GMA26 | GMA25 | GMA24 | GMA23 | GMA22 | GMA21 | GMA20 | RESERVED |   |   |   |

| R/W   | R/W    | R/W                         | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | -        |   |   |   |

| RESET | 0x0000 |                             |       |       |       |       |       |       |       |       |       |       |          |   |   |   |

| ADDR  |        | 0x(FF)FFF108, 10A, 10C, 10E |       |       |       |       |       |       |       |       |       |       |          |   |   |   |

## GMA—Group Mask

These bits mask address A[31:20]. They are used to select the group size. For example, if all the mask bits are cleared, A[31:20] are compared against the value programmed in the group base address register. In this case, the group has a 1M space. If the GMA20 bit is set and the rest of the bits are clear, the group is selected if A[31:21] are the same as the value programmed in the group-base address register. This provides 2M of space for the group. You can decode each chip-select by comparing the lower address lines with the contents of the chip-select option registers. If the memory space for a group of devices is small, you can program the groups to a common space and use the chip-select option registers to decode the areas for each chip-select.

- 0 = For a match to occur, the address line must match the corresponding bit in the GRPBASEx register.

- 1 = The corresponding address line compares true ("don't care").

Bits 0–3—Reserved These bits are reserved. **Chip-Select Logic**

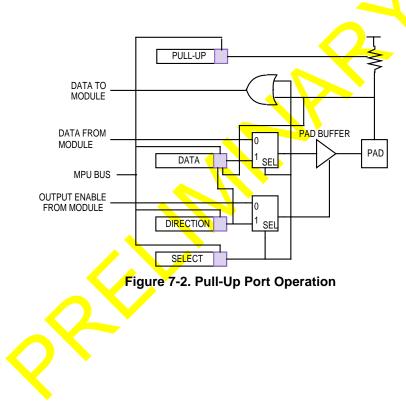

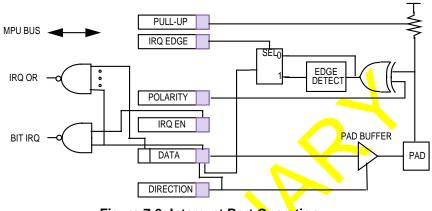

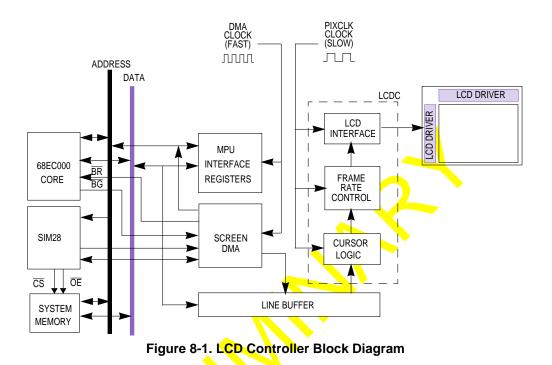

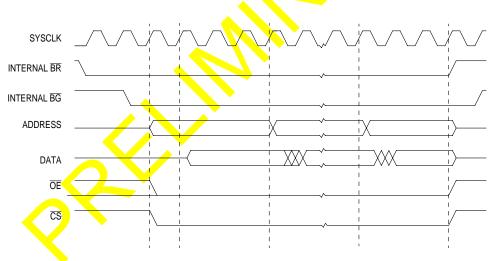

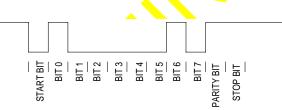

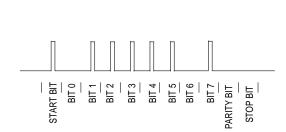

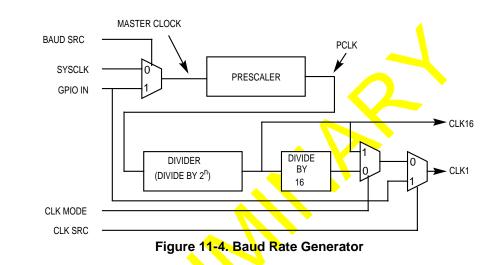

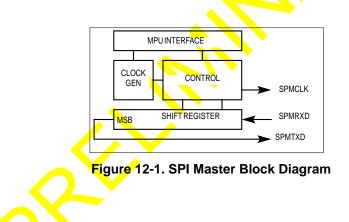

# 5.2.3 Chip-Select Option Registers