# **ÉLECTRONIQUE**

## **Circuits de sélection : multiplexeurs, démultiplexeurs, décodeurs**

### **(Dé)multiplexeurs : plan**

- ▶ multiplexeur

- ◆ principe

- ◆ synthèse d'une fonction logique

- ▶ démultiplexeur

- ▶ décodeurs

- ◆ binaire

- ◆ BCD - 7 segments

# Multiplexeurs : principe

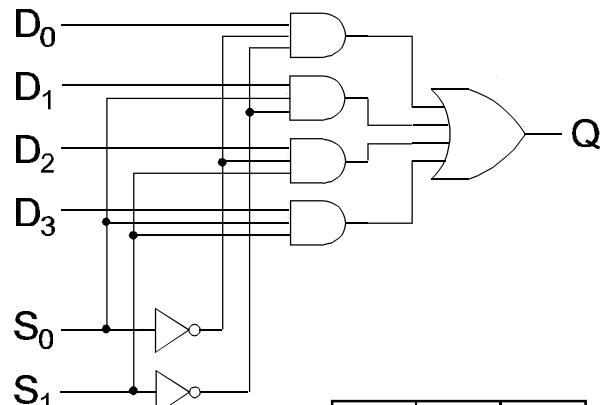

| $S_1$ | $S_0$ | $Q$   |

|-------|-------|-------|

| LO    | LO    | $D_0$ |

| LO    | HI    | $D_1$ |

| HI    | LO    | $D_2$ |

| HI    | HI    | $D_3$ |

Le multiplexeur est un aiguillage numérique à  $2^N$  entrées et 1 sortie. La sortie reflète l'entrée qui porte le numéro codé par les  $N$  bits de sélection  $S_i$ .

La partie droite de la figure montre un multiplexeur "4 vers 1" réalisé à l'aide de 4 portes AND et d'une porte OR, ainsi que la table de vérité correspondante.

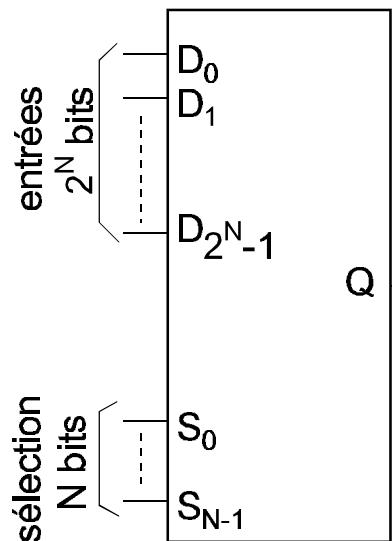

## Multiplexeur : synthèse d'une fonction logique

$$F = \bar{C}B\bar{A} + C\bar{B}A + CBA$$

Toute fonction logique combinatoire pouvant s'exprimer par une somme de produits, un multiplexeur à N entrées de sélection permet synthétiser n'importe quelle fonction F de N variables.

Il suffit d'écrire la table de vérité donnant la valeur de la fonction F pour les  $2^N$  combinaisons possibles des entrées. Ensuite on câble sur chaque entrée du décodeur la valeur de F lue à la ligne correspondante dans la table.

L'exemple montre une fonction de 3 variables ABC, qui peut donc être synthétisée par un multiplexeur 3→8.

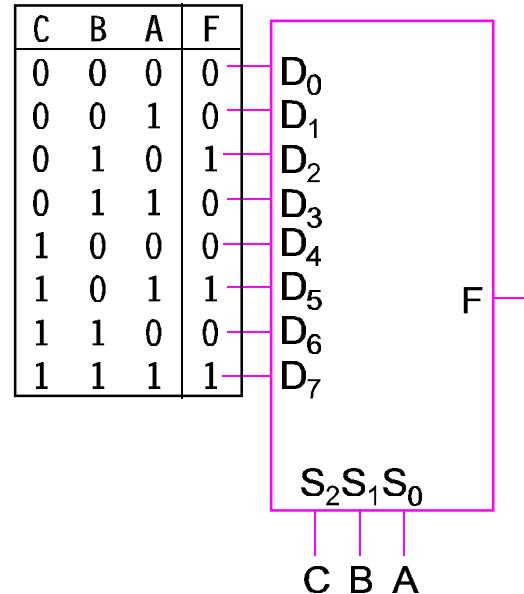

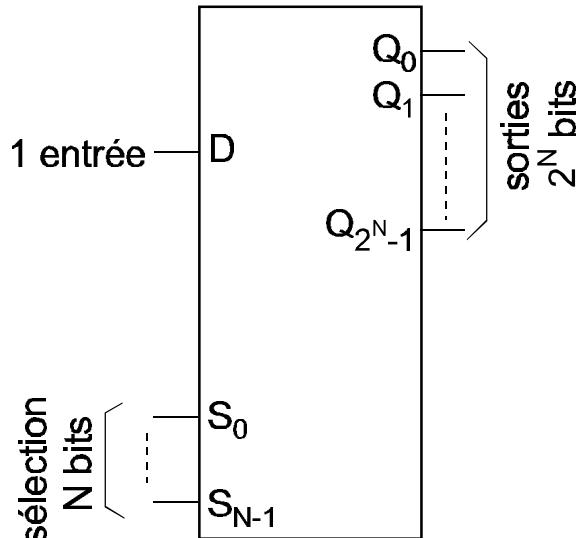

# Démultiplexeur

| S1 | S0 | D  | Q3        | Q2        | Q1        | Q0        |

|----|----|----|-----------|-----------|-----------|-----------|

| LO | LO | HI | LO        | LO        | LO        | <b>HI</b> |

| LO | HI | HI | LO        | LO        | <b>HI</b> | LO        |

| HI | LO | HI | LO        | <b>HI</b> | LO        | LO        |

| HI | HI | HI | <b>HI</b> | LO        | LO        | LO        |

| X  | X  | LO | LO        | LO        | LO        | LO        |

L'aiguillage inverse du multiplexeur est appelé démultiplexeur et possède donc 1 entrée et  $2^N$  sorties. Sa table de vérité est simple :

- si l'entrée D est inactive, aucune sortie n'est active

- si l'entrée D est active, la sortie active est celle dont l'indice est le numéro codé par les bits de sélection ( $S_0, \dots, S_{N-1}$ )

La partie droite de la figure montre l'exemple d'un démultiplexeur "1 vers 4" réalisé à l'aide de portes AND, ainsi que la table de vérité.

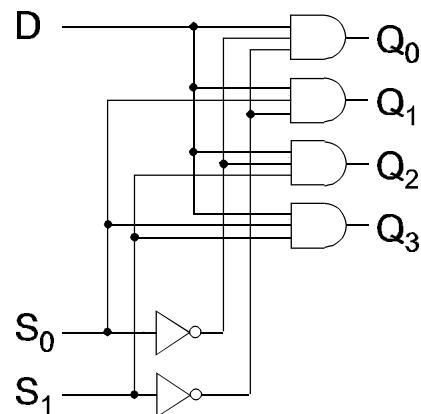

## Décodeur : définition

- ▶ le décodeur a pour fonction de détecter une combinaison particulière de bits (code) à ses entrées et d'activer une combinaison de sorties qui y correspond.

- ▶ décodeur binaire

- ◆ N entrées

- ◆  $2^N$  combinaisons possibles =>  $2^N$  sorties

- ◆ la sortie activée est celle dont l'indice est le nombre codé en binaire à l'entrée

Nous avons vu dans l'introduction que l'on pouvait représenter n'importe quel ensemble de N objets en leur associant un nombre binaire par une opération de codage.

Le décodeur est le circuit logique réalisant l'opération inverse : activer une ou plusieurs sorties logiques si l'on détecte un "mot du code".

Le décodeur binaire en est un cas particulier :

- exhaustif en entrées puisque toutes les  $2^N$  combinaisons des N bits d'entrées sont prises en compte

- simple en sortie puisqu'un seul bit est activé par mot du code d'entrée.

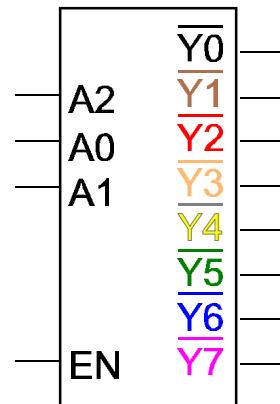

# Décodeur binaire : exemple

## décodeur 3 vers 8

| n | EN | A2 | A1 | A0 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |          |

|---|----|----|----|----|----|----|----|----|----|----|----|----|----------|

| 0 | HI | LO | LO | LO | LO | HI | A2.A1.A0 |

| 1 | HI | LO | LO | HI | HI | LO | HI | HI | HI | HI | HI | HI | A2.A1.A0 |

| 2 | HI | LO | HI | LO | HI | HI | LO | HI | HI | HI | HI | HI | A2.A1.A0 |

| 3 | HI | LO | HI | HI | HI | HI | HI | LO | HI | HI | HI | HI | A2.A1.A0 |

| 4 | HI | HI | LO | LO | HI | HI | HI | HI | LO | HI | HI | HI | A2.A1.A0 |

| 5 | HI | HI | LO | HI | HI | HI | HI | HI | HI | LO | HI | HI | A2.A1.A0 |

| 6 | HI | HI | HI | LO | HI | HI | HI | HI | HI | HI | LO | HI | A2.A1.A0 |

| 7 | HI | LO | A2.A1.A0 |

| X | LO | X  | X  | X  | HI |          |

Le décodeur binaire à 3 entrées présente donc 8 sorties, d'où le nom de décodeur 3-vers-8 ("3-line-to-8-line decoder").

Très souvent, les sorties sont actives à l'état bas. La table de vérité est simple : il n'y a qu'une seule sortie activée : c'est celle dont l'indice est le nombre codé en binaire à l'entrée.

Lorsque l'entrée EN (ENable) est inactive, toutes les sorties sont inactives.

Remarquons que ce décodeur binaire n'est autre qu'un démultiplexeur où l'entrée D joue le rôle de EN et où les sorties sont actives à l'état bas. Il est donc basé sur des circuits NAND (voir dia suivante).

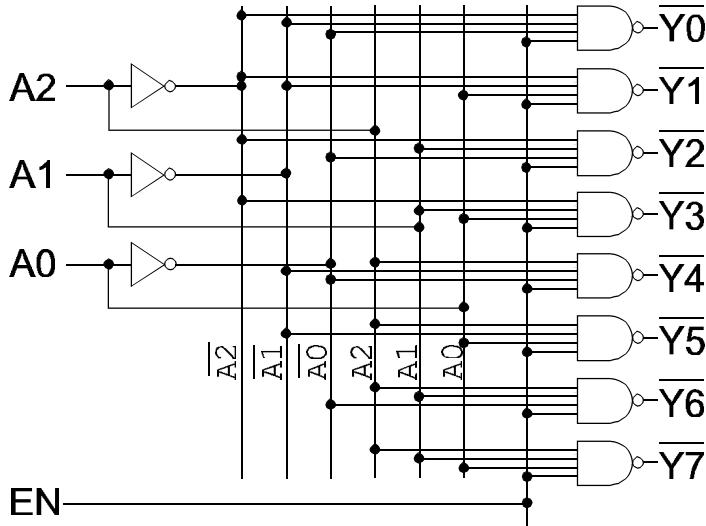

## Décodeur binaire : schéma

! "glitches"

Le décodeur se réalise simplement à l'aide de

- N inverseurs, pour disposer des N entrées et de leurs inverses

- de  $2^N$  portes NAND à  $(N+1)$  entrées, réalisant les produits logiques présentés dans la table de vérité précédente et l'activation par le signal EN.

Désactiver l'entrée supplémentaire EN bloque toutes les sorties à l'état inactif (HI).

Un tel décodeur présente nécessairement des transitoires parasites en sortie dont la durée est de l'ordre du temps de propagation des inverseurs d'entrée. En effet les NAND de sortie recombinent des signaux qui ont suivi des chemins logiques de longueur différente (suivant qu'ils sont ou non passés par un inverseur). Le temps de propagation spécifié pour le décodeur doit donc nécessairement tenir compte du délai maximum pour que toutes les sorties soient stables (seule l'une d'entre-elles étant à l'état actif).

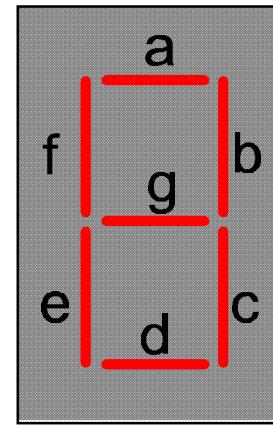

# Décodeur BCD- 7 segments

- n'utilise pas toutes les combinaisons d'entrées (10/16)

- fournit 7 bits en sortie

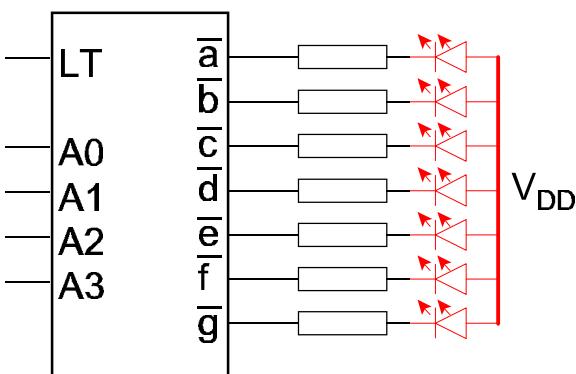

Un exemple de décodeur où toutes les combinaisons d'entrées ne sont pas prises en compte et où il y a plus d'un bit de sortie activé est le décodeur BCD vers 7-segments.

Il est destiné à transformer un chiffre décimal codé en binaire (c'est-à-dire un nombre de 4 bits restreint aux valeurs de 0 à 9) en niveaux de commande pour afficheurs à diodes électro-luminescentes (LED). Le cas illustré ici est celui d'un afficheur à anode commune.

L'anode commune est reliée à l'alimentation positive  $V_{DD}$ . Chaque cathode est en série avec une résistance de limitation du courant (10 à 20 mA par segment). Une sortie du décodeur active à l'état bas allume le segment correspondant.

Une entrée supplémentaire LT (Lamp Test) permet d'allumer inconditionnellement tous les segments.

L'étudiant aura l'occasion d'utiliser de tels décodeurs au laboratoire. On écrira la table de vérité à titre d'exercice.

Remarquons que l'on peut convenir de symboles à afficher pour les combinaisons des entrées A3...A0 allant de 1010 à 1111.

Pourrait-on représenter lisiblement les 16 chiffres hexadécimaux ?