# ÉLECTRONIQUE

## Introduction au 8051

## 8051: Plan de l'introduction

- ▶ Pourquoi étudier le 8051 ?

- ▶ Schéma-bloc simplifié du 8051

- ▶ Alimentation et horloge

# Pourquoi étudier le 8051? (1)

## ► popularité

- ◆ facilement disponible (>10 fabricants)

- ◆ large support d'outils hard/soft (gratuits et payants)

- ◆ énorme expérience accumulée

## ► efficacité

- ◆ architecture conçue pour le contrôle-commande

## ► pérennité

- ◆ existe depuis 1985

- ◆ encore de belles années devant lui

## ► simple mais pas trivial

- ◆ permet l'étude

- d'une unité centrale simple

- de la plupart des périphériques

Né au milieu des années 1980, le micro-contrôleur 8051 - et les nombreux dérivés qui ont été développés depuis -ont pris une large part de marché dans les applications de contrôle-commande numérique.

C'est une famille très populaire, produite par plus de 10 fabricants, et pour laquelle il existe une base énorme d'outils de développement, aussi bien en matériel qu'en logiciel.

Beaucoup de développeurs ont acquis une expérience qui contribue à perpétuer son usage.

C'est un bon exemple pour l'étude des microprocesseurs, car il est à la fois suffisamment simple pour être didactique, et suffisamment complexe pour offrir un bon échantillonnage des différents périphériques et des propriétés classiques d'autres processeurs simples.

## Pourquoi étudier le 8051 ? (2)

### ► amélioration technologique constante

#### ◆ design du Si

- transistors plus petits ("shrink"),  $f \nearrow$

- $V_{\text{lim}} \searrow$  et consommation  $\searrow$

#### ◆ boîtiers

- 40 pattes "Dual-In-Line" à l'origine

- tendances plus modernes

- montage de surface

- densité élevée de pattes

- épaisseur très faible

- "gros" boîtiers ( $>80$  pattes) pour beaucoup d'I/O

- très petits boîtiers ("tiny"  $<20$  pattes) pour peu d'I/O et grande compacité

## Pourquoi étudier le 8051 ? (3)

### ► toute une famille

- ◆ "noyau dur" et jeu d'instruction communs

- ◆ ajout de périphériques

- augmentation des I/O

- nouvelles fonctions

- nécessite surtout de nouveaux registres internes

- facile à prendre en compte en logiciel

- ◆ code largement compatible

- ◆ il y en a presque toujours un 8051 mieux adapté pour un problème donné

- ◆ outils, programmes, formation et savoir-faire sont largement réutilisables

- ◆ intégration dans des SoC (System-on-a-chip)

Ce qui fait l'unité de tous les processeurs dérivés du 8051, c'est leur noyau commun de ressources matérielles et leur jeu d'instruction.

Sur cette base, les constructeurs ont développé des dizaines de variantes, essentiellement par l'ajout de périphériques supplémentaires pour augmenter le nombre d'entrées-sorties et pour donner de nouvelles fonctionnalités. Ces développements ont été portés par des applications de grosses productions, qui permettent d'amortir les frais de développement.

Les nouveaux périphériques nécessitent évidemment des registres supplémentaires d'entrée-sortie et de configuration; l'adaptation des outils de développement logiciels se limite le plus souvent à faire reconnaître les noms des nouveaux registres spéciaux, ce qui se fait par une simple modification de fichiers de configuration.

Quelques variantes modernes ont apporté des améliorations plus profondes, comme l'augmentation du nombre de pointeurs vers les données (voir leçon sur les modes d'adressage), dont les compilateurs et assembleurs ont évidemment dû tenir compte.

Les outils de développement en matériel et en logiciel, la formation du personnel, l'expérience des développeurs et le code existant pour un processeur de la famille peuvent être largement récupérés sur des processeurs ultérieurs (même d'autres fabricants), ce qui a certainement contribué au succès de la famille.

Signalons enfin que le noyau 8051 est également présent dans des plates-formes combinant dans le même boîtier

- logique programmée (c'est-à-dire microprocesseur exécutant un programme)

- logique programmable (exécutions "hardware" par des circuits logiques standards dont le "câblage" est changé par un programme)

On parle alors de System on a Chip (SoC).

## 8051: Plan de l'introduction

- ▶ Pourquoi étudier le 8051 ?

- ▶ **Schéma-bloc simplifié du 8051**

- ▶ Alimentation et horloge

# 8051 : schéma-bloc (mode µC)

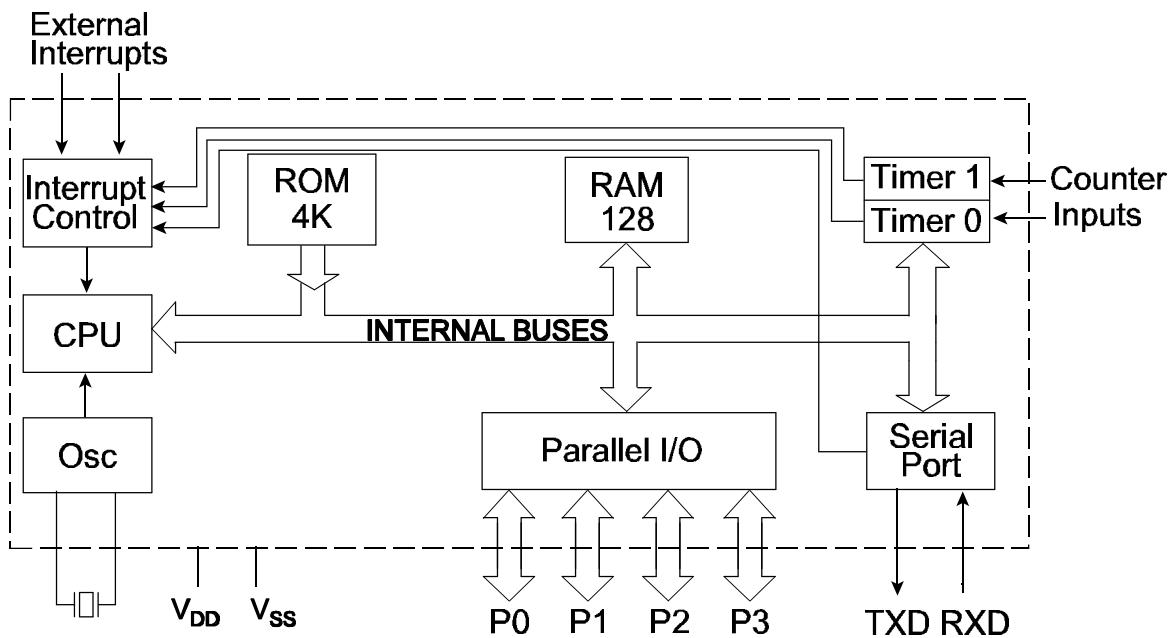

Nous avons ici un schéma-bloc simplifié du 8051 en mode micro-contrôleur (le mode micro-processeur sera vu ultérieurement).

L'unité centrale (CPU) est cadencée par un oscillateur d'horloge (OSC). Le CPU communique, via des bus internes, avec ses mémoires:

- la mémoire programme accessible en lecture (ROM)

- la mémoire pour les données accessible en lecture-écriture (RAM).

Le CPU est assisté par plusieurs périphériques, qu'il peut configurer et avec lesquels il peut évidemment échanger des données. On voit sur la figure :

- un groupe de périphériques d'entrées-sorties parallèles (PARALLEL I/O) regroupées en 4 blocs de 8 bits appelés PORTS (P0, P1, P2, P3)

- deux "Timers" (TIMER0 et TIMER1) qui sont en fait des compteurs destinés à compter soit des périodes de l'horloge interne, soit des événements externes.

- un port de communication série ("SERIAL PORT") bidirectionnel

Ces périphériques peuvent interrompre le fonctionnement du programme, via des lignes d'interruption, pour provoquer le traitement des données dont ils sont responsables.

Les différentes bornes du boîtier sont consacrées :

- à l'alimentation (V<sub>DD</sub>, V<sub>SS</sub>)

- au quartz externe de l'oscillateur, qui n'est évidemment pas intégrable

- aux entrées-sorties en parallèle et en série

- aux interruptions externes

On remarquera que l'ordre de grandeur des ressources disponibles en interne dans le 8051 (comme dans plupart des micro-contrôleurs simples) n'a rien avoir avec celui des micro-ordinateurs usuels. On dispose le plus souvent de

- quelques Ko ou quelques dizaines de Ko de ROM

- quelques dizaines à quelques centaines d'octets de RAM

Les applications de tels micro-contrôleurs sont donc des tâches simples, pour lesquelles on recherche essentiellement un bon rapport coût/performances (avec un prix pouvant descendre à quelques Euros).

## 8051: Plan de l'introduction

- ▶ Pourquoi étudier le 8051 ?

- ▶ Schéma-bloc simplifié du 8051

- ▶ **Alimentation et horloge**

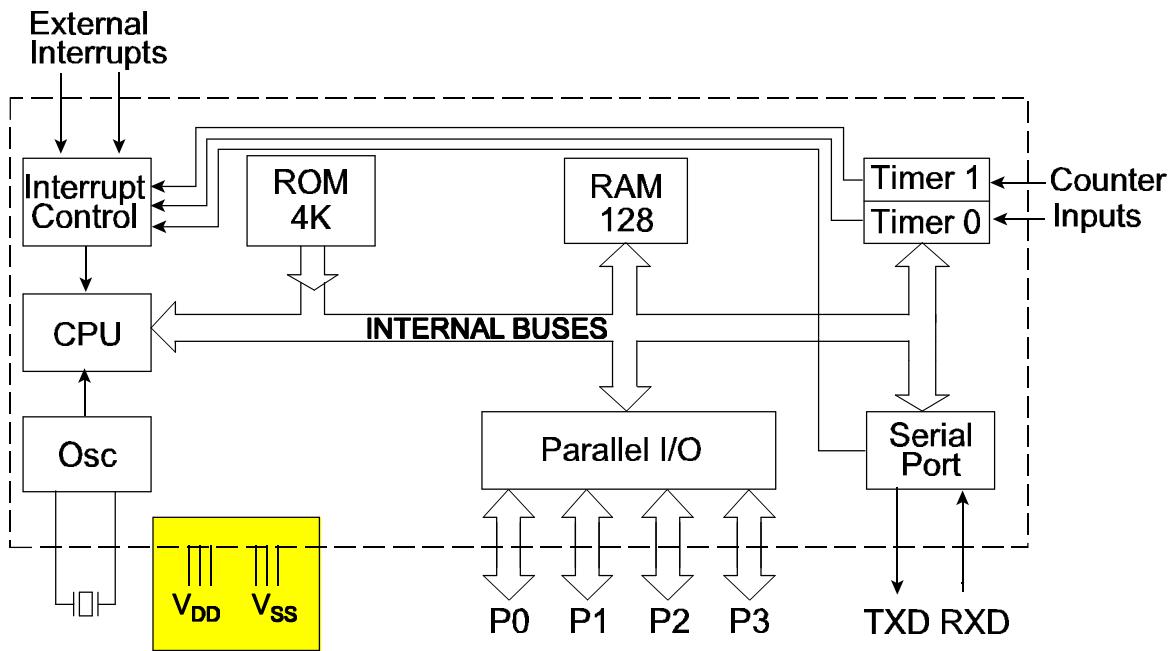

# 8051 : alimentation

L'alimentation est évidemment essentielle. Sur les processeurs modernes, l'alimentation par deux bornes ( $V_{DD}$  et  $V_{SS}$ ) est en général insuffisante pour garantir une distribution à basse impédance dans toute la pastille de silicium.

Il y a donc souvent plusieurs bornes d'alimentation et de masse.

## Alimentation des µP (1)

- ▶ consommation en fonctionnement

- ◆ petits µC : qq 100µA .. qq 10mA

- ◆ µP 64 bits : qq A à qq 10 A (dépend de  $V^2 \cdot f$ )

- ▶ modes de consommation réduite

- ◆ économie globale d'énergie, systèmes sur batterie

- ◆ qq µA

- ◆ parfois en plusieurs stades

- ▶ tendances

- ◆ diminuer la tension : 5V, 3.3V, 2.8V, 2.5V,...1.2V

- ◆ multi-tensions (5V ou 3.3V pour I/O, <2.5V CPU)

Se préoccuper de la consommation est un phénomène récent pour les micro-processeurs utilisés dans les micro-ordinateurs.

Depuis toujours, les micro-contrôleurs sont par contre optimisés pour une très faible consommation. Ils sont donc bien adaptés aux systèmes sur piles ou batteries. La plupart possèdent plusieurs stades de réduction de consommation.

Avec l'évolution technologique, la tendance est à la baisse de la tension d'alimentation, ainsi qu'aux alimentations multiples (par exemple 3.3V pour les entrées sorties et 2.5V, voire moins, pour le cœur)

## Alimentation des µP (2)

- ▶ fluctuations rapides de consommation

- ◆  $di/dt >>$

- ◆ précautions d'alimentation

- distribution soignée à faible impédance

- pistes larges

- plans de masse et d'alimentation

- découplage soigné de chacune des bornes d'alimentation

Nous avons évoqué dans un précédent chapitre les difficultés d'alimentation des systèmes logiques. Les systèmes à microprocesseurs ne font pas exception. Le microprocesseur lui-même est souvent un des plus gros consommateurs de la carte sur laquelle il se trouve; il doit donc être particulièrement bien alimenté, via des pistes de largeur suffisante, avec un bon découplage de toutes les bornes d'alimentation.

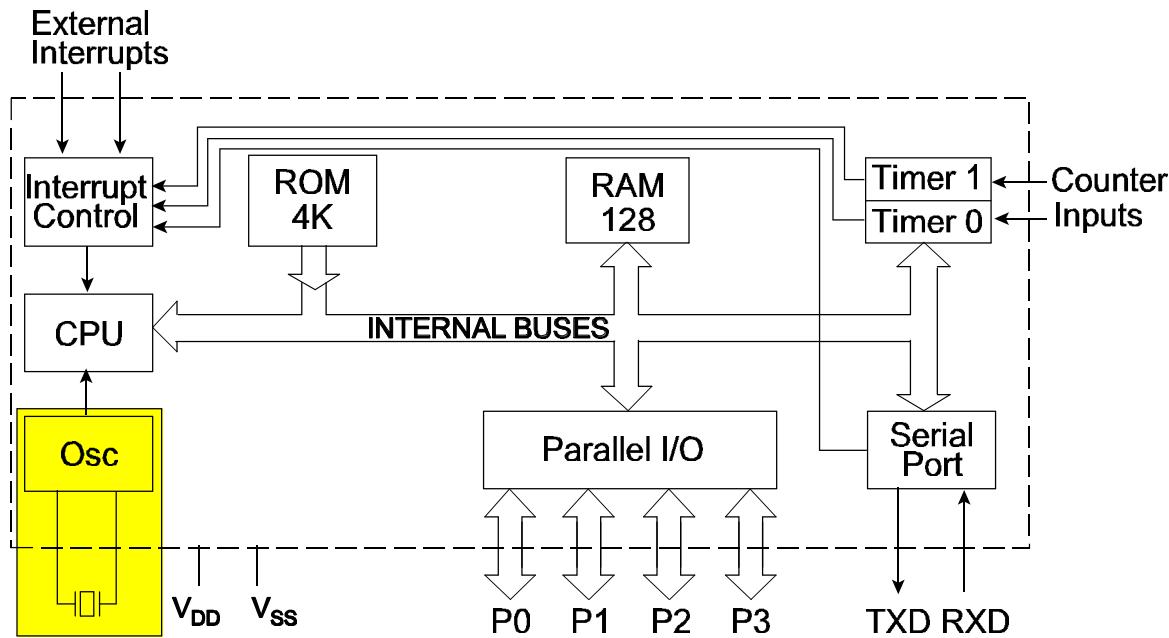

# 8051 : horloge

La grande majorité des systèmes à microprocesseur sont cadencés par une horloge. Un multivibrateur astable peut remplir ce rôle, mais avec une stabilité de fréquence médiocre. Dans beaucoup d'applications, il est intéressant de disposer d'un signal d'horloge stable, notamment pour mesurer précisément des intervalles de temps. Les microprocesseurs incorporent donc un amplificateur permettant de réaliser un oscillateur à quartz bon marché, avec une précision relative de l'ordre de 10<sup>6</sup>. Cette précision est relativement médiocre par rapport aux meilleurs oscillateurs, mais largement suffisante pour la plupart des applications.

Nous allons examiner les principes de tels oscillateurs sur base de celui du 8051.

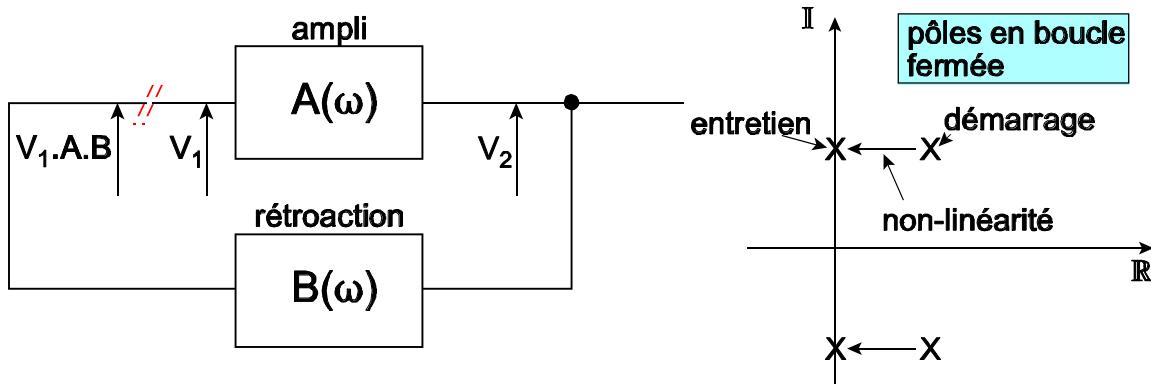

## Oscillateur d'horloge : rappels

- **démarrage de l'oscillation au départ du bruit de fond**

- **croissance exponentielle de l'amplitude si**

$A(\omega).B(\omega) \geq 1$  avec  $\phi_A + \phi_B = 0$  ou  $360^\circ$

- **entretien de l'oscillation :**

$A(\omega).B(\omega) = 1$  par non-linéarité

Pour rappel, un oscillateur se compose d'un amplificateur de gain  $A(\omega)$ , muni d'une rétroaction de gain  $B(\omega)$ .

En toute généralité,  $A$  et  $B$  sont complexes, c'est-à-dire qu'ils introduisent à la fois un changement d'amplitude et de phase, en fonction de la fréquence.

S'il existe une fréquence à laquelle le produit des deux gains  $AB$  est un **réel positif supérieur à l'unité**, toute perturbation à l'entrée y revient en phase et amplifiée par le gain  $AB$ . L'oscillation naît alors au départ du bruit de fond et son amplitude croît exponentiellement.

Pour que l'oscillateur soit stable, il faut encore que, une fois l'amplitude désirée atteinte, une non-linéarité agisse sur le produit  $AB$  pour le ramener à l'unité et l'y maintenir; l'amplitude de l'oscillation reste alors constante.

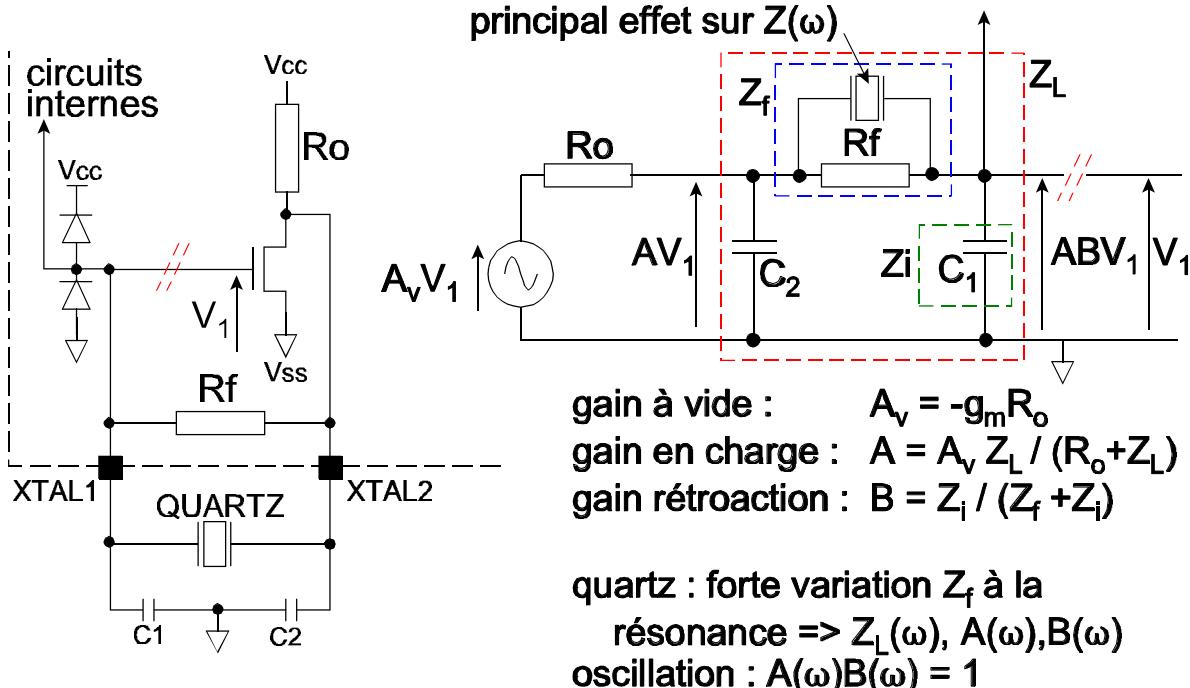

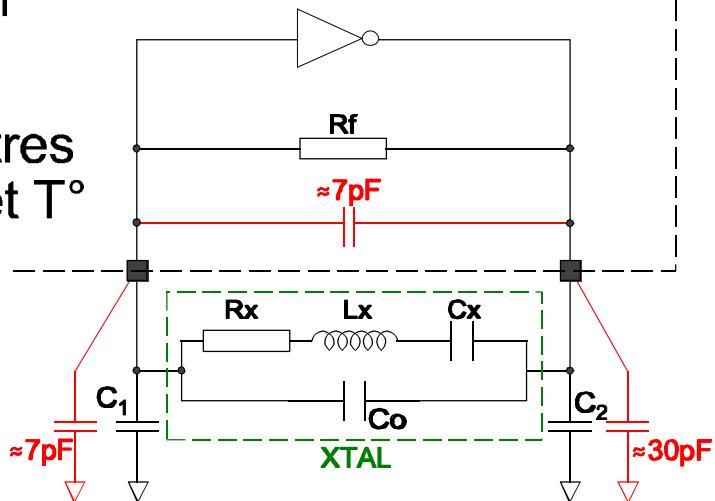

# Oscillateur d'horloge du 8051

Dans une des variantes du 8051, l'oscillateur est construit sur base d'un étage amplificateur à transistor NMOS.

Coupons par la pensée la rétroaction au niveau de la grille (voir traits de coupure sur la figure). Soit une perturbation d'amplitude  $V_1$  sur la grille. Si la sortie n'était pas chargée, on obtiendrait un gain à vide

$$A_v = -g_m \cdot R_o$$

L'étage est donc une source de tension d'amplitude  $A_v \cdot V_1$  et d'impédance de sortie  $R_o$ .

Vu cette impédance de sortie, le gain en charge  $A$  est plus faible que le gain à vide; il est déterminé par le diviseur d'impédance formé par  $R_o$  et l'impédance de charge  $Z_L$  (définie sur la figure); la tension de drain vaut alors  $A \cdot V_1$ .

La fraction de cette tension de drain qui est ramenée à la grille est déterminée par le diviseur d'impédance formé par  $Z_f$  et  $Z_i$ , définissant ainsi le gain de rétroaction  $B$ .

La base de l'oscillation est le quartz qui présente une variation d'impédance très importante avec la fréquence (voir diapos suivantes) et influence donc à la fois les gains  $A$  et  $B$ .

Compte tenu d'un déphasage de  $180^\circ$  introduit par l'amplificateur à transistor, le circuit de rétroaction doit fournir un supplément de  $180^\circ$  pour ramener à la grille un signal en phase. Si l'on ôte le quartz, les cellules RC introduisent chacune un déphasage de moins de  $90^\circ$ , ce qui est insuffisant. Le rôle du quartz est donc de provoquer un déphasage supplémentaire, d'où le nom d'oscillateur à réactance positive.

Le signal de sortie est la tension de grille, qui est distribuée à l'intérieur du microprocesseur. La non-linéarité qui limite l'amplitude est ici constituée d'un circuit d'écrêtage à diode qui "clampe" la tension entre les bornes d'alimentation.

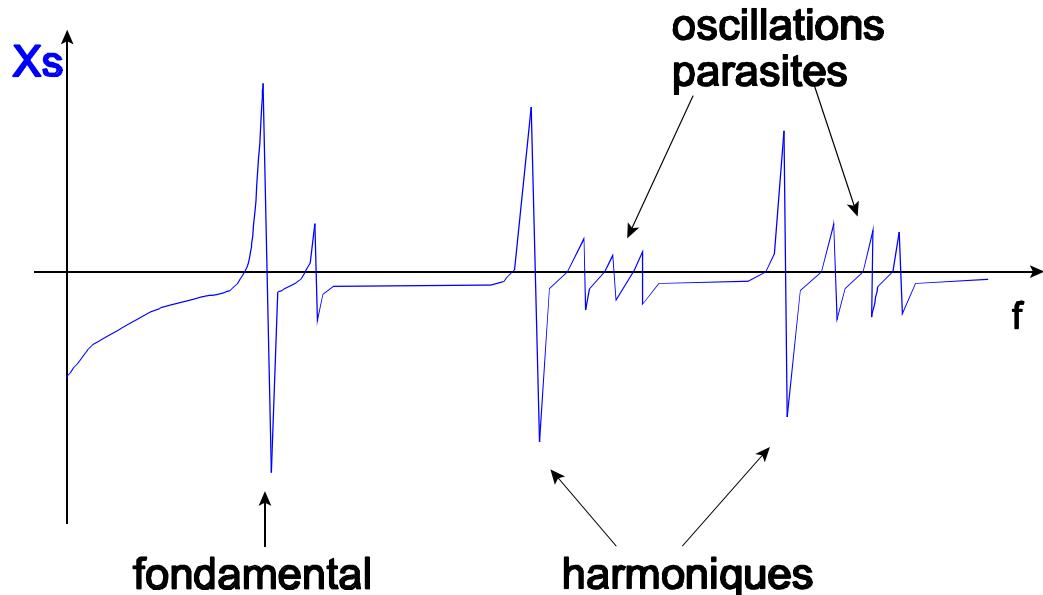

## Oscillateur d'horloge : réactance d'un quartz

Le quartz est un cristal piézoélectrique. L'effet piézoélectrique réversible, lié à la structure cristalline, consiste en :

- l'apparition de charges sur un cristal soumis à une tension mécanique (cisaillement, compression)

- l'apparition d'une déformation mécanique lorsque le cristal est soumis à un champ électrique.

Pour connecter le cristal dans un circuit électrique, on en métallise 2 faces parallèles pour former des électrodes, auxquelles on soude des fils. Le circuit extérieur est destiné à exciter électriquement un des modes de vibration mécaniques.

Du point de vue électrique, les résonances mécaniques se marquent par des variations brutales de la réactance. Les oscillateurs fonctionnent normalement sur le premier mode de vibration (fondamental).

## Oscillateur d'horloge (4)

Si l'on s'intéresse de plus près à la résonance principale (fondamental) et que l'on relève les caractéristiques électriques du circuit, on peut donner un schéma équivalent formé :

- d'un circuit résonant R-L-C série

- en parallèle sur un condensateur qui représente la capacité propre du cristal ainsi que la capacité de la monture (c'est-à-dire les deux électrodes métalliques).

L'intérêt des quartz vient

- de la bonne stabilité de leur fréquence de résonance avec la température (les oscillateurs ultra-stables doivent néanmoins être thermostatisés)

- du caractère très aigu de la résonance, avec un coefficient de qualité de plusieurs dizaines de milliers !

On obtient deux fréquences de résonance très proches :

- la résonance série  $\omega_s$ , où la réactance s'annule et le quartz est équivalent à la résistance  $R_x$  de quelques dizaines d'Ohm.

- la résonance parallèle  $\omega_p$ , où la réactance s'annule et le quartz présente une résistance très élevée.

Il existe plusieurs schémas d'oscillateurs qui exploitent l'une ou l'autre de ces résonances.

On remarque la variation très brutale de la réactance autour de la résonance parallèle.

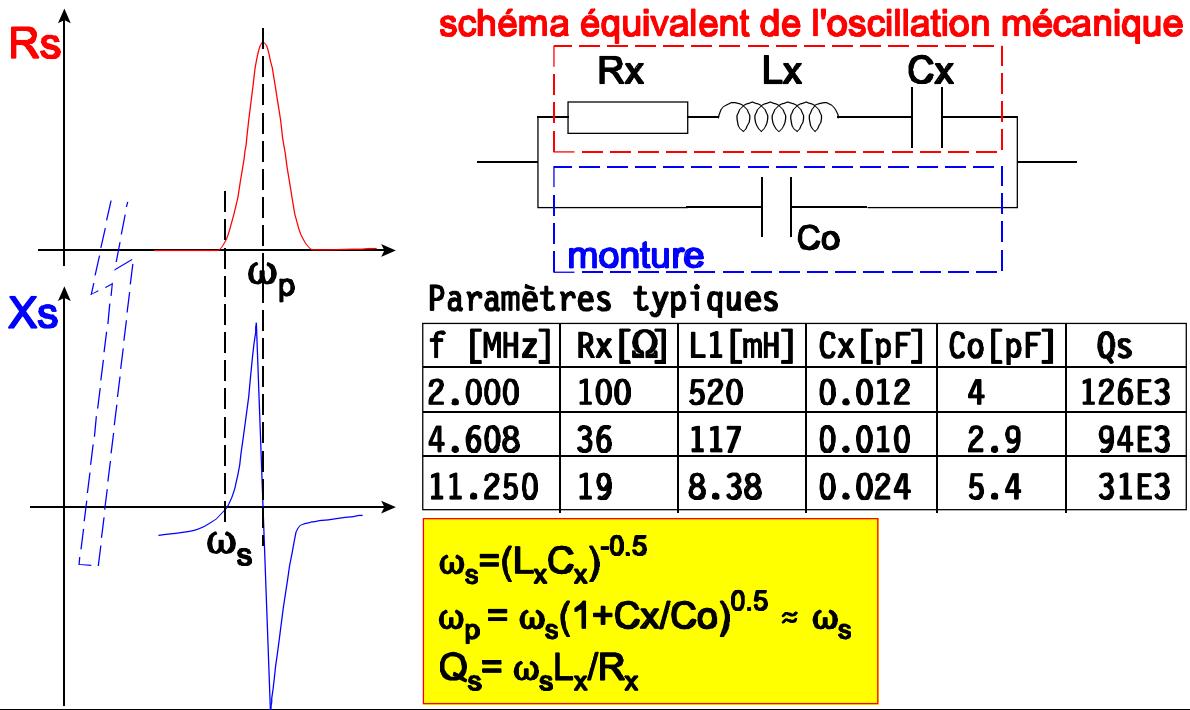

## Oscillateur d'horloge : évolution du gain en boucle ouverte

Cette figure donne les courbes de gain et déphasage en boucle ouverte de l'oscillateur du 8051, avec un quartz de 4.6MHz .

La bande passante (largeur du pic de résonnance à -3dB) est très étroite (<1mHz), ce qui montre bien que l'oscillation ne peut se produire qu'au voisinage de la résonance du quartz.

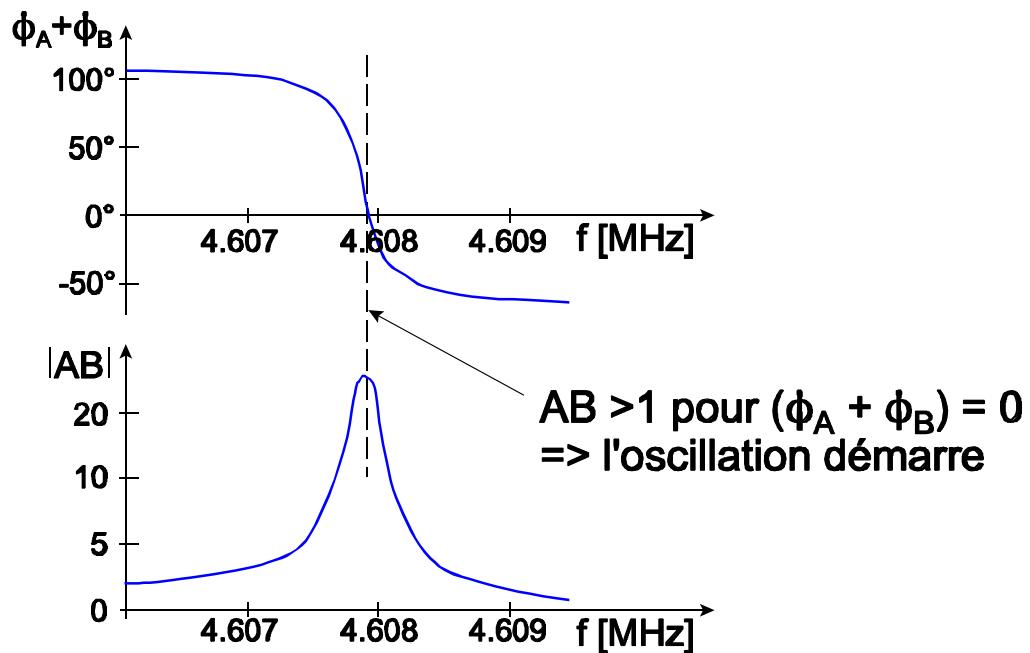

## Oscillateur d'horloge : phénomènes parasites

### ► condensateurs parasites

- ◆ participent à l'oscillation

- ◆ valeur mal connue

- variables ( $T^\circ, V$ )

- dispersion de fabrication

- variantes

- ◆ **plutôt gênants**

### ► variation des paramètres du transistor avec $V$ et $T^\circ$

L'oscillation peut être perturbée par les condensateurs parasites à l'entrée, à la sortie et la capacité "Miller" drain-grille du NMOS.

Ces condensateurs font partie intégrante du processus d'oscillation, mais sont en général mal connus et varient dans une fourchette assez sensible avec la dispersion de fabrication, la tension d'alimentation et la température.

S'y ajoutent les variations des caractéristiques du transistor.

Il faudra donc s'assurer du bon fonctionnement de l'oscillateur dans toute la plage de variation de tension (en particulier dans les systèmes sur pile) et de température.

## Oscillateur d'horloge : rôle de C1 et C2

### ► C1 et C2 ↗

#### ◆ favorable

- ↗ rôle des capas parasites

- ↗ AB pour les harmoniques

#### ◆ défavorable

- ↗ temps de démarrage

- ↗ amplitude oscillation

### ► valeurs usuelles : 20-80pF

### ► performances

#### ◆ précision

- 0,1% à 1% (souvent suffisant !)

- avec ajustage 0.005%

#### ◆ stabilité = 0.05%

Le coefficient de qualité est une mesure du rapport entre l'énergie fournie par le transistor à chaque période (pour maintenir l'amplitude de l'oscillation en compensant les pertes) et l'énergie stockée dans les réactances du circuit oscillant.

Vu le coefficient de qualité très élevé des quartz, le temps démarrage de l'oscillation peut être de plusieurs dizaines de ms, chaque période d'oscillation n'apportant qu'une fraction de l'énergie réactive.

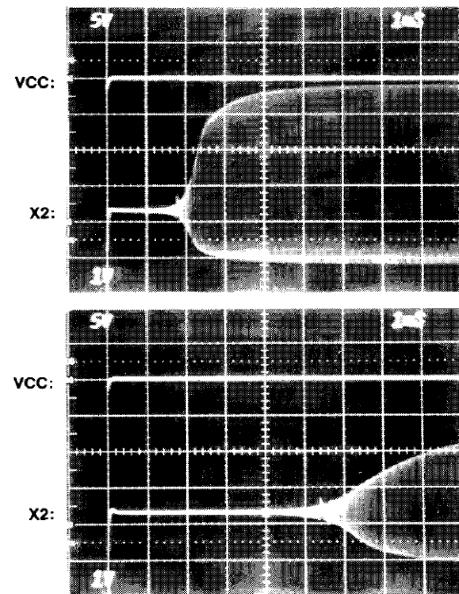

Les oscillosogrammes représentent le démarrage de l'oscillation, avec différentes valeurs des capacités externes  $C_1$  et  $C_2$ .

Grossir les condensateurs  $C_1$  et  $C_2$  :

- diminue l'influence des capacités parasites qu'elles shuntent

- diminue le gain AB à fréquence élevée, ce qui limite le risque d'osciller sur un harmonique

- augmente le temps de démarrage

- diminue l'amplitude de l'oscillation

On peut également se servir de condensateurs fixes ou variables pour retoucher légèrement la fréquence d'oscillation (c'est le cas dans les montres par exemple).

# Oscillateur d'horloge : problèmes fréquents

| problème            | cause                     | remède(s)                                                |

|---------------------|---------------------------|----------------------------------------------------------|

| f trop grande       | accrochage sur harmonique | ↗ Ci                                                     |

| f trop faible       | oscillation parasite      | ↘ Ci, soigner le câblage                                 |

| démarrage incertain | gain AB trop faible       | ↘ Ci, soigner câblage<br>changer de quartz ( $R_X \ll$ ) |

|                     | "noise pick-up"           | soigner découplage<br>soigner câblage                    |

Le tableau ci-dessus résume les principaux problèmes que l'on peut rencontrer pour faire osciller le quartz de manière fiable et qui ont déjà été décrits.

La marge de manœuvre est assez réduite, puisque le schéma de l'oscillateur est imposé par le constructeur.

Les ennuis viennent souvent

- d'un mauvais choix du quartz (la résistance  $R_X$  de certains quartz est parfois trop élevée).

- d'un mauvais dimensionnement de  $C_1$  et  $C_2$

- de couplages parasites de l'oscillateur avec d'autres signaux voisins ("noise pick-up").

On consultera toujours la notice du processeur, qui précisera le schéma à adopter et fournira éventuellement des prescriptions sur

- le type de quartz (voir même une ou plusieurs marques et types qui ont été testés)

- les valeurs de  $C_1$  et  $C_2$

## Oscillateur d'horloge : règles de bonnes pratique

### ► soigner le câblage

#### ◆ éviter les couplages inductifs

- quartz très proche du  $\mu$ P: diminuer les boucles

- XTAL1- quartz-XTAL2

- XTALi - Ci - Vss (i=1..2 )

#### ◆ éviter les couplages capacitifs

- éloigner pistes à  $dv/dt$  élevé

- entourer de pistes "calmes" (Vss,Vcc bien découplés)

- mettre le boîtier du quartz à la masse

### ► ajuster $C_1$ et/ou $C_2$

#### ◆ obtenir une amplitude crête-à-crête $\geq V_{cc}/2$

#### ◆ ! oscilloscope peut tuer oscillation ( $Z_{in}=10M\Omega/qq\text{ pF}$ )

- $R_{in}$  perturbe polarisation XTAL1 => mesure en AC

- si  $C_{in}$  perturbe XTAL2 alors diminuer  $C_2$

Le bon fonctionnement de l'oscillateur nécessite un câblage soigné. En particulier, les inductances de connexion sont des éléments parasites à limiter autant que possible. Il faut donc

- rapprocher le quartz le plus possible du processeur

- prévoir une piste de masse proche du quartz pour y connecter les condensateurs  $C_1$  et  $C_2$

Les couplages capacitifs ("pick-up" ou diaphonie) entre pistes voisines peuvent être polluants; on évitera donc de faire voisiner sur de grandes longueurs :

- deux pistes d'horloges différentes

- une piste de l'oscillateur et une piste véhiculant un autre signal présentant des flancs très raides

- une piste d'horloge et une piste véhiculant un signal analogique de faible amplitude

On peut entourer les pistes "à risque" de pistes à faible  $dv/dt$  comme la masse et l'alimentation (avec un découplage soigné bien sûr). Le boîtier du quartz est métallique et peut être mis à la masse, mais c'est une opération difficile si on le monte verticalement pour gagner de la surface.

La valeur maximum de  $C_1$  et  $C_2$  est fixée par le souci de maintenir une amplitude d'oscillation supérieure à la moitié de la tension d'alimentation, et ce sur toute la plage de température. La mesure de cette amplitude à l'oscilloscope est susceptible de perturber :

- la polarisation du transistor (si le signal utile est à la grille du NMOS) par la résistance d'entrée de la sonde (même de l'ordre de  $10M\Omega$ ); il est recommandé de faire la mesure en couplage AC

- la valeur de  $C_1$  et  $C_2$ ; si l'on veut ajuster  $C_1$  et  $C_2$  de manière précise, il faudra retoucher les valeurs pour tenir compte des quelques pF introduits par la sonde.

Le cas échéant, la présence de la sonde peut tuer l'oscillation.

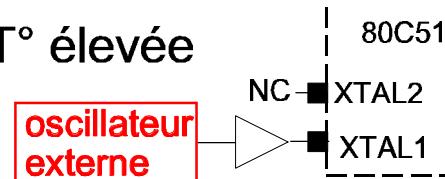

# Oscillateur d'horloge externe

## ► buts

- ◆ augmenter la stabilité (rarement indispensable)

- ◆ augmenter la sortance

- ◆ démarrage sûr avec plage de  $T^\circ$  élevée

- ◆ facilité de mise en oeuvre

- pas d'ajustage

- oscillateur blindé

## ► toujours vérifier la notice du $\mu$ P

- ◆ entrée sur XTAL1 ou XTAL2 ?

- ◆ niveau de tension (surtout si alimentation multiple) ?

- ◆ buffer intermédiaire ?

On trouve dans le commerce des oscillateurs relativement peu onéreux et tout faits, sous forme de petits boîtiers qui contiennent le quartz et l'amplificateur. Ils fournissent un signal qui peut être injecté tel quel au processeur (après une mise en forme éventuelle par une porte logique).

On connecte l'oscillateur externe à la place du quartz, ou, plus exactement, à une des bornes XTAL1 ou XTAL2 prévues pour le quartz, l'autre borne restant non connectée. Il n'y a pas de règle universelle pour connaître la borne d'entrée, car il existe plusieurs schémas d'oscillateurs internes. On consultera donc toujours la notice, même pour des processeurs apparentés.

Le recours à un oscillateur externe est un peu plus cher, mais c'est une facilité qui évite la mise au point du circuit d'horloge, en particulier :

- la vérification du fonctionnement sur toute la plage de température

- les problèmes de démarrage

- les couplages capacitifs, ces oscillateurs étant montés dans un boîtier métallique blindé

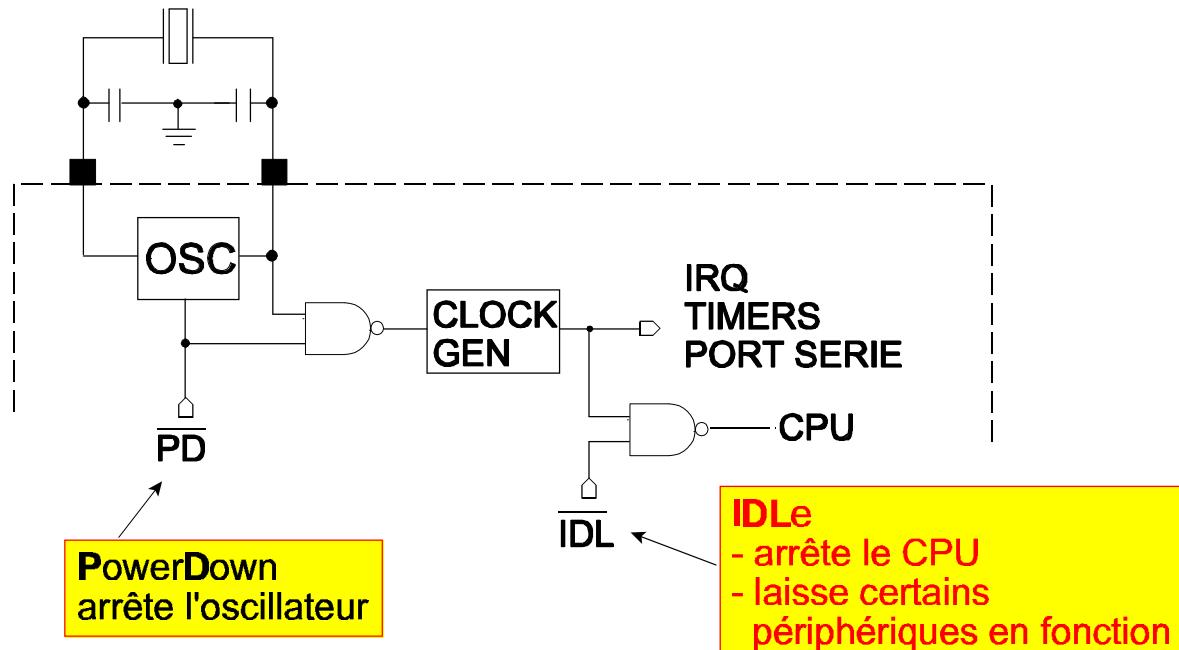

# Oscillateur d'horloge : économie d'énergie

Comme la consommation des processeurs CMOS est proportionnelle à la fréquence, l'oscillateur est un des éléments clés de l'économie d'énergie.

Dans le cas des variantes modernes du 8051, deux bits de commande contrôlés par le déroulement du programme sont prévus :

- PD (Power Down) arrête complètement l'oscillateur

- IDL' (IDLe) arrête l'unité centrale mais laisse certains périphériques en fonction

Pour que le système fonctionne, il faut évidemment que l'économie d'énergie soit désactivée automatiquement lors de la mise sous tension, et lors d'un RESET.

On sort généralement du mode d'économie d'énergie lors d'un événement (interruption) externe ou interne. Un des cas fréquents d'événements internes est le réveil régulier par un "timer" pour effectuer une tâche périodique, qui se termine par la mise en sommeil du processeur. Le timer doit donc continuer à être alimenté et recevoir son signal d'horloge en permanence.

Certains micro-contrôleurs sont beaucoup plus sophistiqués que le 8051 à cet égard, avec une grande variété de "stades de sommeil" (voir par exemple le MSP430 de Texas Instruments)